VHDL-Web-Projekte zum Lehrbuch: Technische Informatik 2: Entwurf digitaler Schaltungen.

|

Das Buch enthält in der Regel nur die wichtigen Code-Ausschnitte der Beispielbeschreibungen.

Auf dieser Web-Seite stehen die zugehörigen kompletten Programmdateien und

Testrahmen, getestet mit dem Simulator ghdl.

Den Simulator gibt es sowohl für Linux als auf für Windows

hier frei im Web. Er ist auch

auf den Rechnern im Übungsraum installiert, die während der

betreuten Laborzeiten genutzt werden. Für die graphische Signaldarstellung

ist zusätzlich GTKWave zu installieren.

Die Beschreibungen

zu den Web-Projekten stehen im Script und Hinweise zur Übersetzung und Ausführung

sind in der jeweiligen Hilfe-Datei zum Projekt zu finden.

|

Zum Experimentieren mit den im Buch beschrieben VHDL-Entwürfen ist das nachfolgende zip-Archiv auf den Rechner herunterzuladen und mit Verzeichnissen zu entpacken. Es enthält alle im Buch beschriebenen Dateien und zusätzlich für jeden Abschnitt einen Hilfetext mit den Befehlen zur Durchführung der Simulation und zur Visualisierung der Ergebnisse. Die gleichfalls enthaltenen Sav-Dateien enthalten die Visualisierungseinstellungen für GTKWAVE (angezeigte Signale, angezeigtes Zeitfenster etc.). Die Bibliothek Tuc ist bereits übersetzt im Archiv enthalten, so dass der Abschnitt zur Bibliothek übersprungen werden kann. Es sei empfohlen, für jedes Beispiel die Beschreibung im Buch zu lesen, die vorbereiteten Simulationen auszuprobieren und danach mit den Beispielen zu experimentieren (Veränderung und Erweiterung der Testeingaben, Änderung der beschrieben Funktionen und Strukturen etc.). Viel Spass beim Experimentieren!

Zip-Archiv mit allen Dateien: [zip_EVHDL.zip]

Zu den einzelnen Kapiteln:

ENTRY:TUC_Hilfe (versteckt)

GHDL-Kommandofolge zur Erzeugung und zum Test der Bibliothek TUC

|

ENTRY:TUC_Ausgabe (versteckt)

Textausgabe (Tuc.Ausgabe)

Package

Testrahmen

|

ENTRY:TUC_Stop (versteckt)

Kontrollierter Simulationsabbruch (Tuc.StopSim_pack)

Package

Testrahmen

|

ENTRY:TUC_Eingabe (versteckt)

Textausgabe (Tuc.Ausgabe)

Package

Testrahmen

|

ENTRY:TUC_Numerik (versteckt)

Arithmetische Operationen (Tuc.Numeric_Sim und Tuc.Numeric_Synth)

Package für die Simulation

Testrahmen Package für die Simulation

Arithmetische Operationen (Tuc.Numeric_Sim und Tuc.Numeric_Synth)

Package für die Synthese

Testrahmen für das Package für die Synthese

|

ENTRY:TUC_Zufallstest (versteckt)

Pseudo-Zufallstest (Tuc.Zufallstest)

Package

Testrahmen

|

ENTRY:HalloWelt (versteckt)

Erstes ausführbares VHDL-Programm

Hilfe zum Übersetzen und Ausführen

|

ENTRY:HalloWelt1 (versteckt)

Erweitertes Programm unter Nutzung eines Packages

Das Package dazu

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Anfangswerte (versteckt)

Test der Anfangswerte von Variablen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_SimX (versteckt)

Logische Vernüpfung mit X

Hilfe zum Übersetzen und Ausführen

|

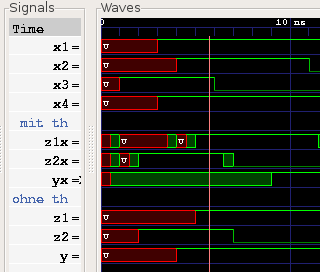

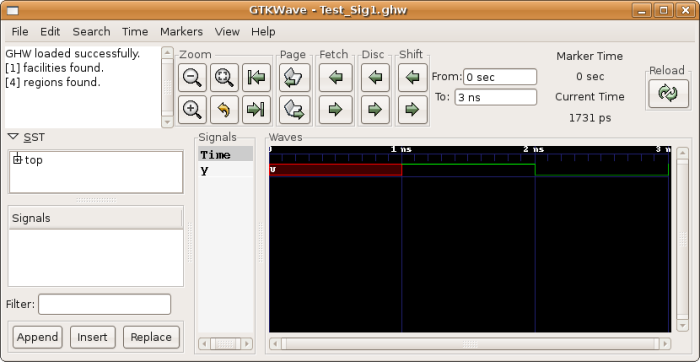

ENTRY:Test_Sig1 (versteckt)

Test einer einzelnen Signalzuweisung

Hilfe zum Übersetzen und Ausführen

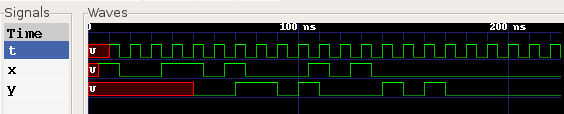

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

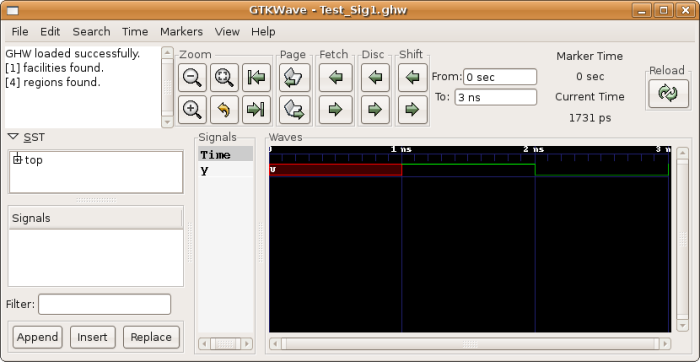

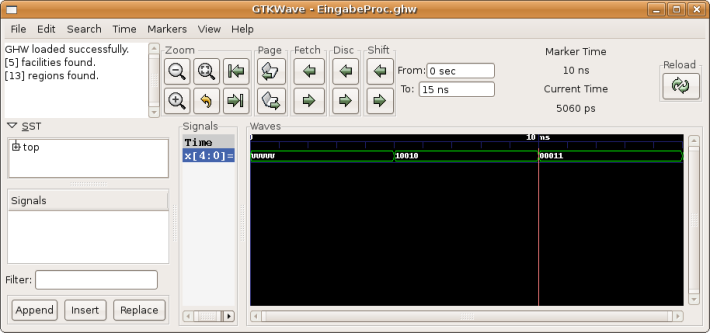

ENTRY:EingabeProc (versteckt)

Prozess zur Erzeugung eines Testeingabesignals

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

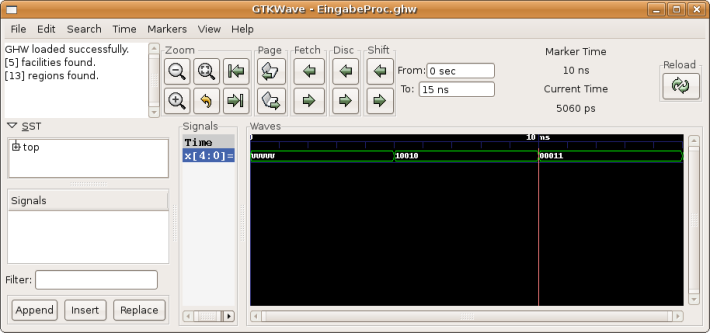

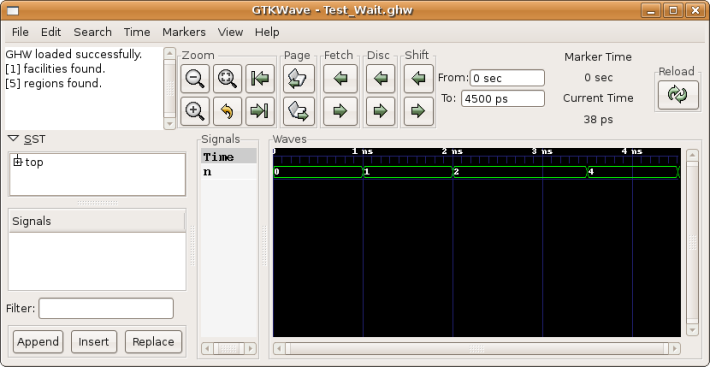

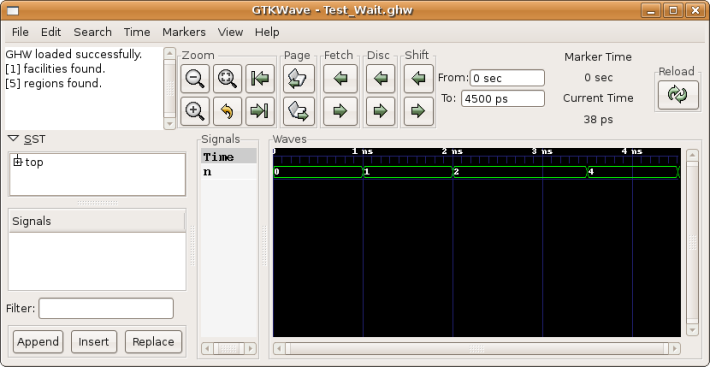

ENTRY:Test_Wait (versteckt)

Prozess zur Erzeugung eines Testeingabesignals

Hilfe zum Übersetzen und Ausführen

Textausgaben während der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

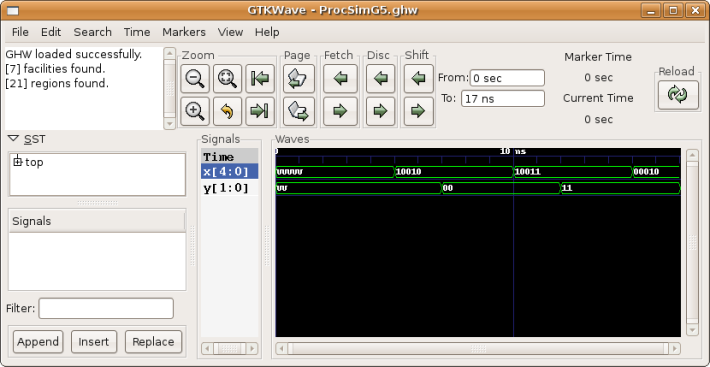

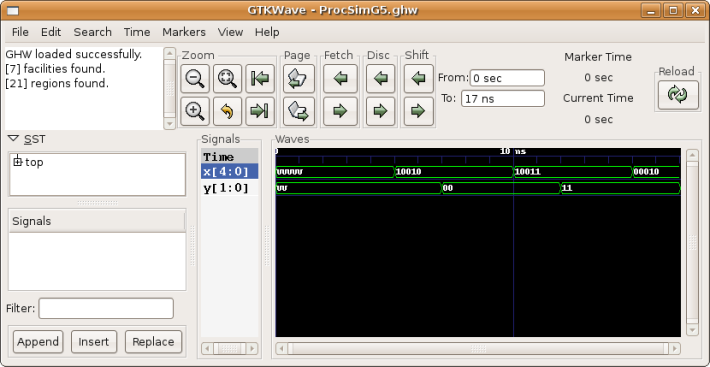

ENTRY:ProcSimG5 (versteckt)

Prozess zur Erzeugung eines Testeingabesignals

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

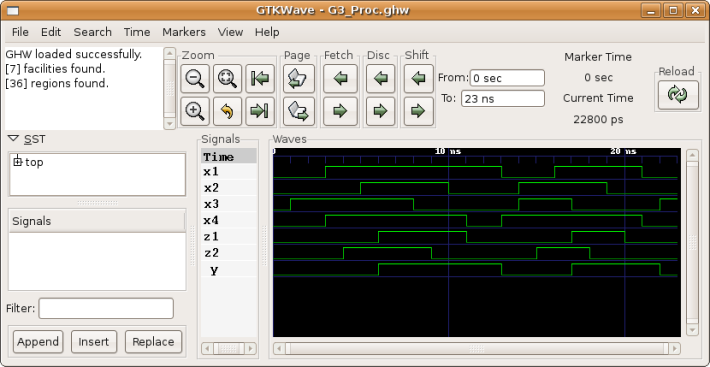

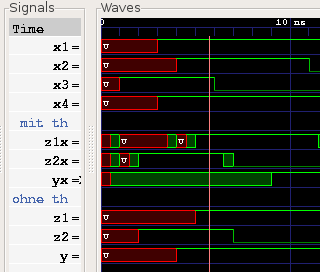

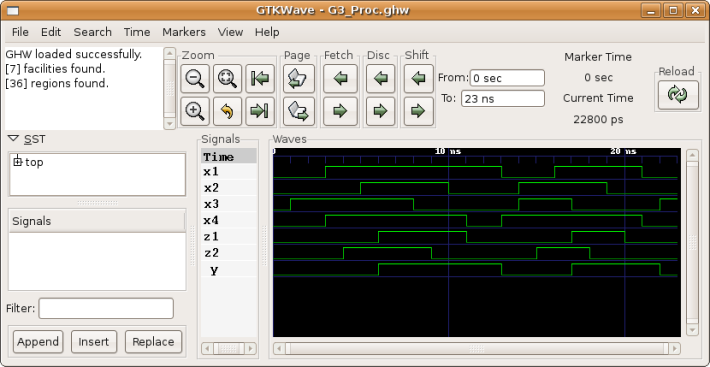

ENTRY:G3_Proc (versteckt)

3-Gatterschaltung mit einem Prozess je Gatter

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

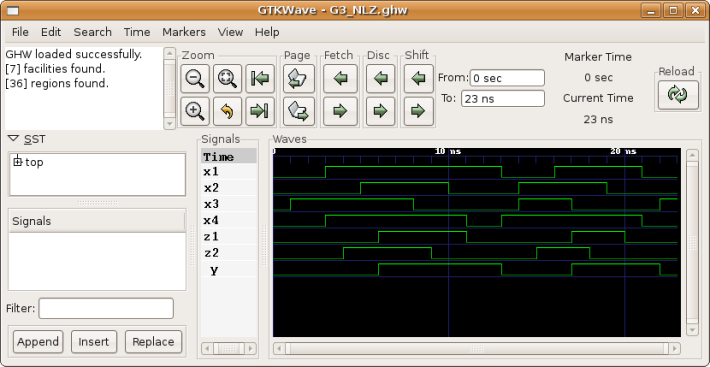

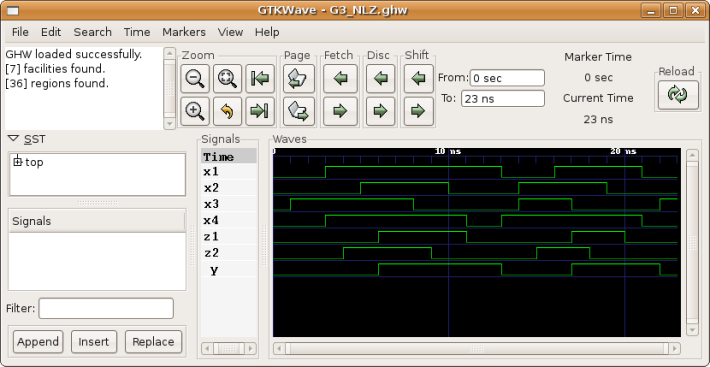

ENTRY:G3_NLZ (versteckt)

3-Gatterschaltung mit einer nebenläufigen Signalzuweisung je Gatter

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

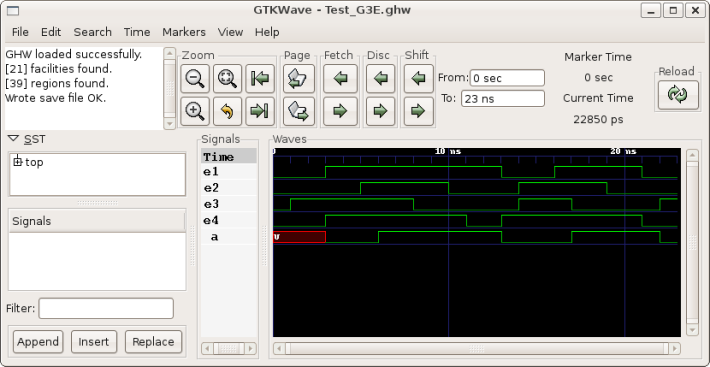

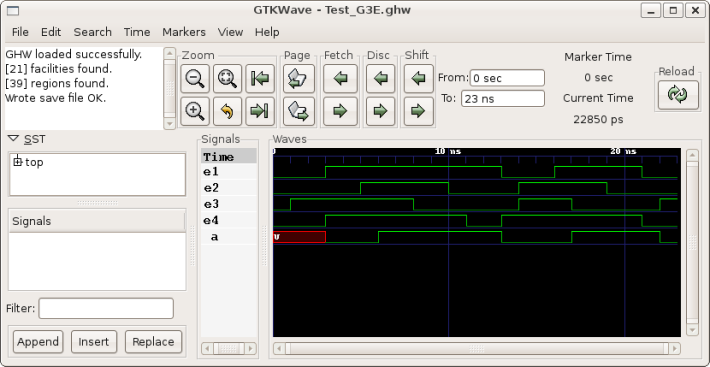

ENTRY:Test_G3E (versteckt)

Strukturbeschreibung der 3-Gatter-Schaltung

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

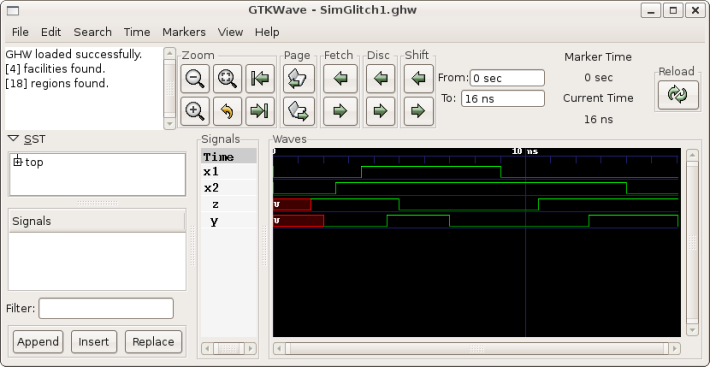

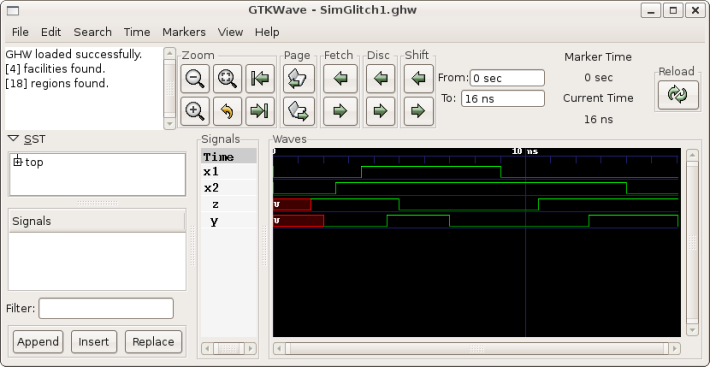

ENTRY:SimGlitch1 (versteckt)

Kontrolle der Signalverläufe in Abb. 1.37

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

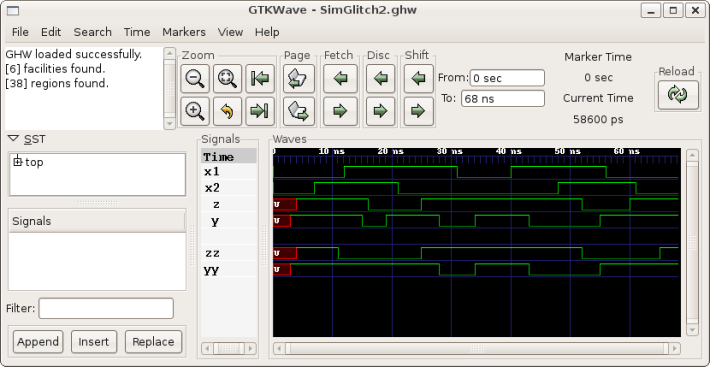

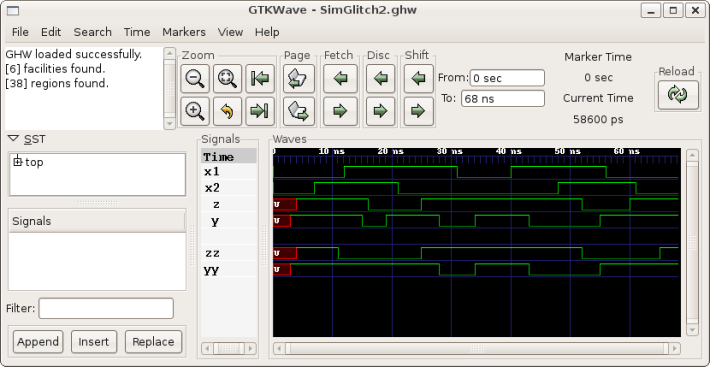

ENTRY:SimGlitch2 (versteckt)

Kontrolle der Signalverläufe in Abb. 1.38

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

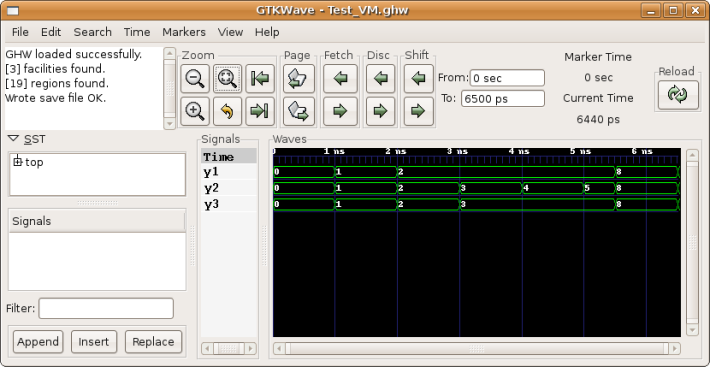

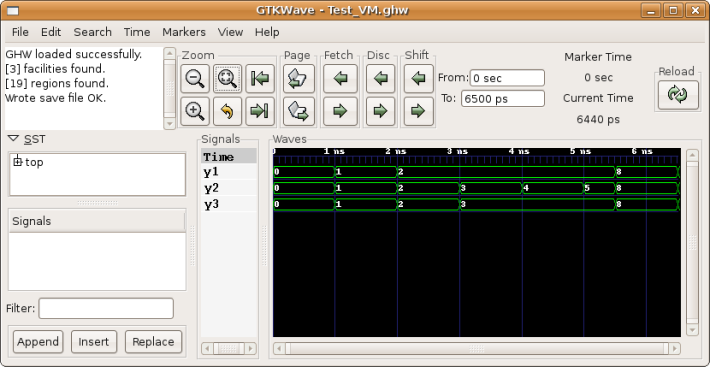

ENTRY:Test_VM (versteckt)

Test der Wirkung der Verzögerungsmodelle

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

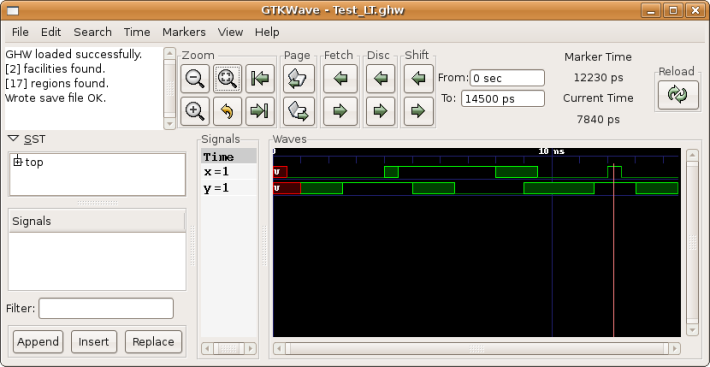

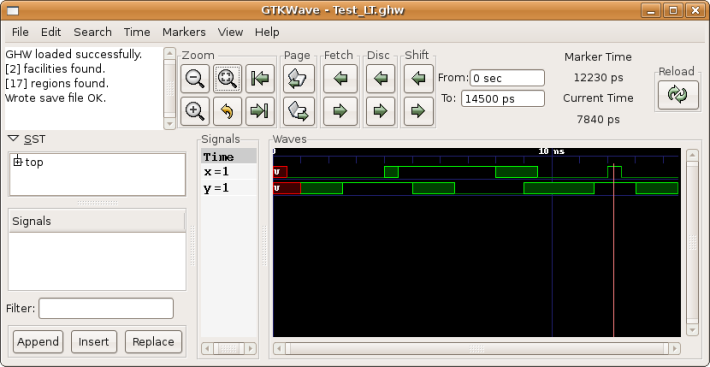

ENTRY:Test_LT (versteckt)

Test der Wirkung der Verzögerungsmodelle

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

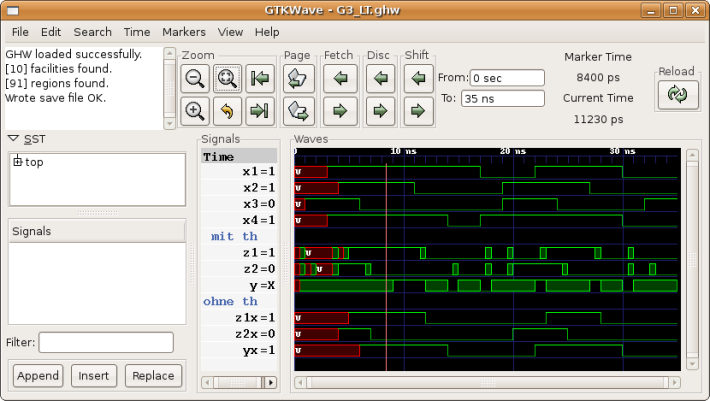

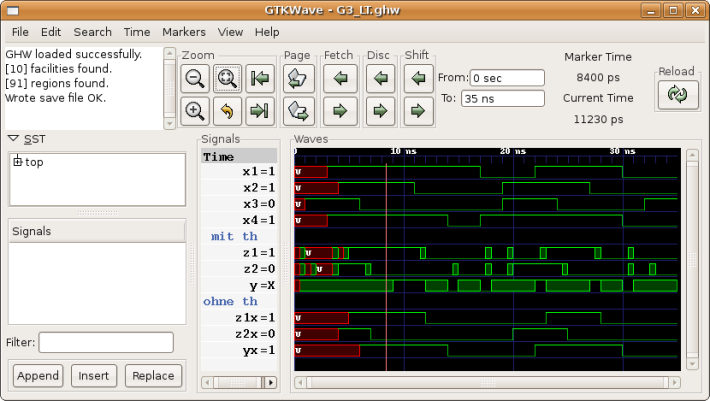

ENTRY:G3_LT (versteckt)

Test der Wirkung der Verzögerungsmodelle

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

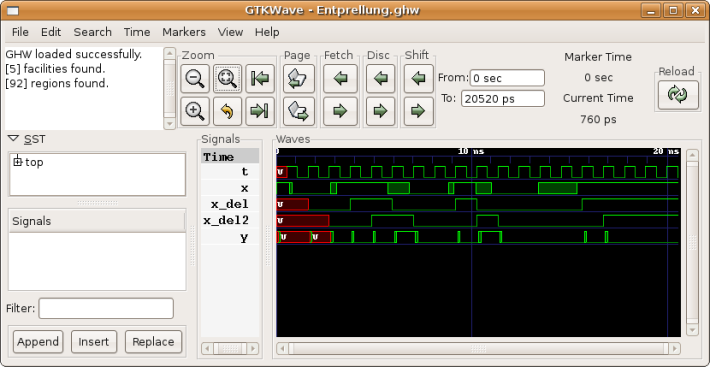

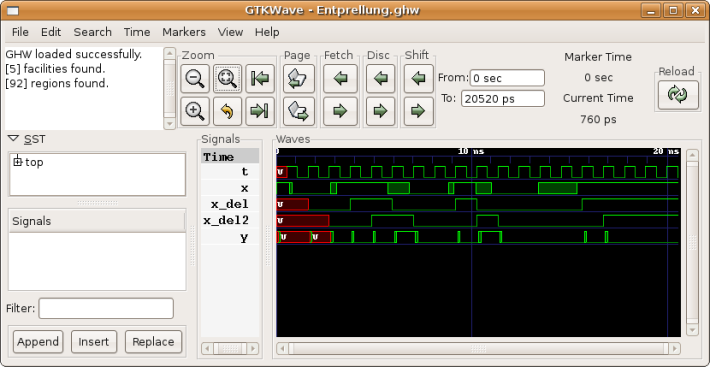

ENTRY:Entprellung (versteckt)

Entprellen und Flankenerkennung für eine Tasteneingabe

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

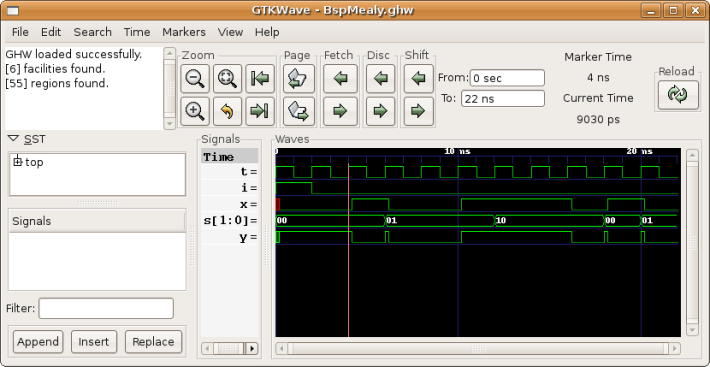

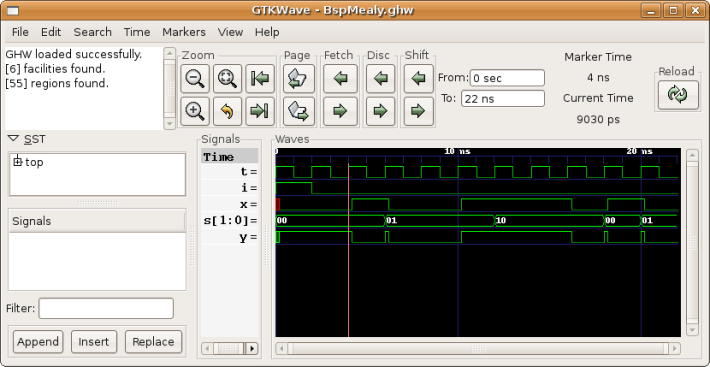

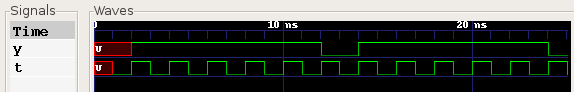

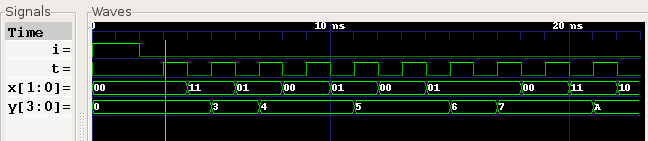

ENTRY:BspMealy (versteckt)

Mealy-Automat

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

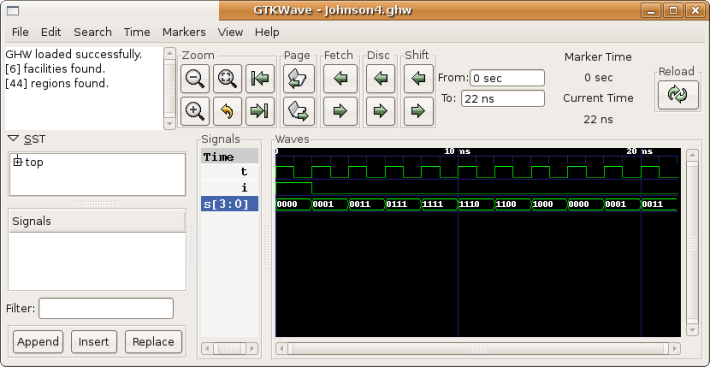

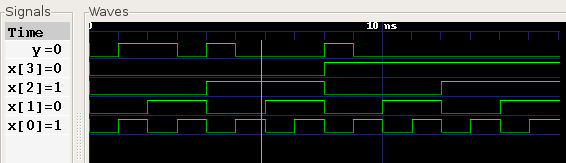

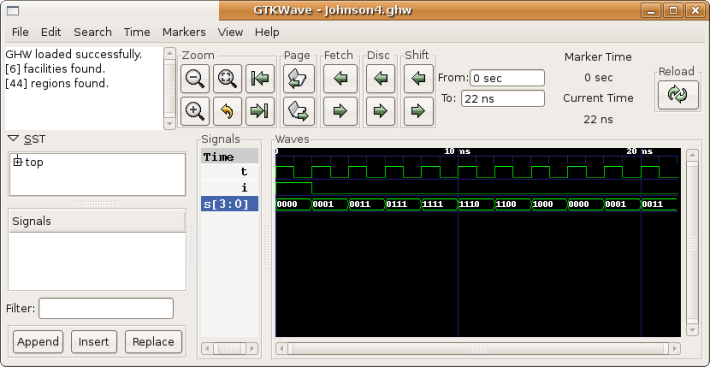

ENTRY:Johnson4 (versteckt)

Johnson-Zähler

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

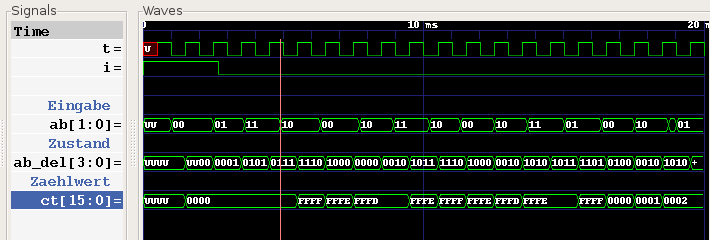

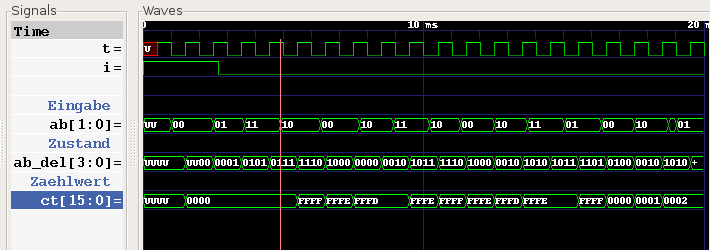

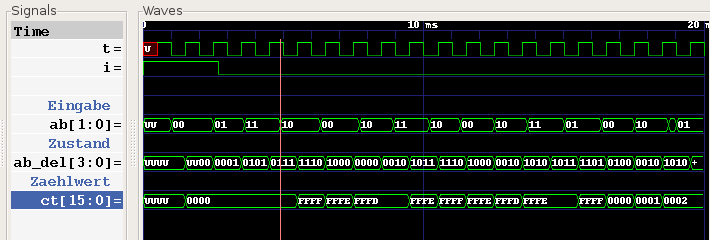

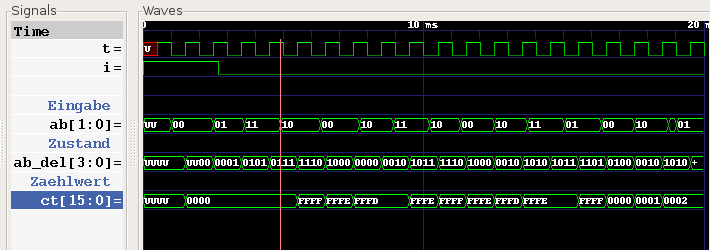

ENTRY:Zahlenschloss (versteckt)

Zahlenschloss

Hilfe zum Übersetzen und Ausführen

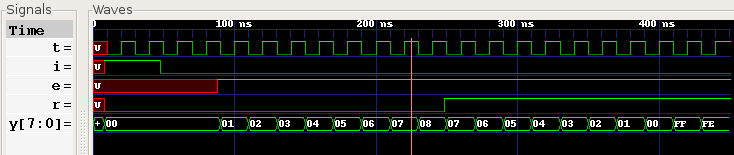

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

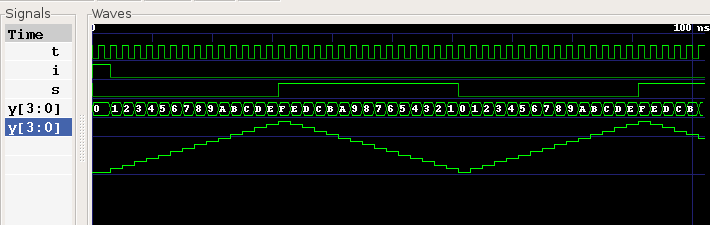

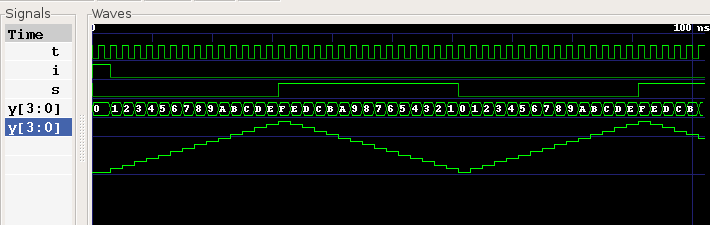

ENTRY:DreieckGen (versteckt)

Dreiecksignalgenerator

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

Das generierte Dreiecksignal ist zweimal dargestellt, einmal hexadezimal und einmal analog.

|

ENTRY:QuadEnc (versteckt)

Quadraturencoder

Testrahmen für den Quadraturencoder

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

Die Bibliothek TUC stellt für die Beispiele im Buch Datentypen und Unterprogramme

für die Ein- und Ausgabe, für arithmetische Operationen, die kontrollierte Beendigung

der Simulation mit mehreren Prozessen und für die Bereitstellung von

Pseudo-Zufallstests bereit. Sie enthält die nachfolgenden Packages.

1.1 Modellbildung und Simulation

1.1.4 VHDL als formale Beschreibungsplattform

1.2 Funktion, Struktur und Simulation

1.2.3 Imperative Funktionsmodelle

1.2.4 Ereignisgesteuerte Simulation

1.2.5 Strukturbeschreibung; 1.2.6 Testrahmen

1.3 Laufzeittoleranzen

1.3.1 Glitches

1.3.2 Das Verzögerungsmodell einer Signalzuweisung

1.3.3 Simulation mit Halte- und Verzögerungszeiten

1.5 Asynchrone Eingabe

1.5.2 Entprellen von Tasten

1.6 Sequentielle Schaltungen

1.6.2 Vom Zustandsgraph zur VHDL-Beschreibung

1.6.4 Entwurf eines Zahlenschlosses

1.6.5 Operationsablaufgraph

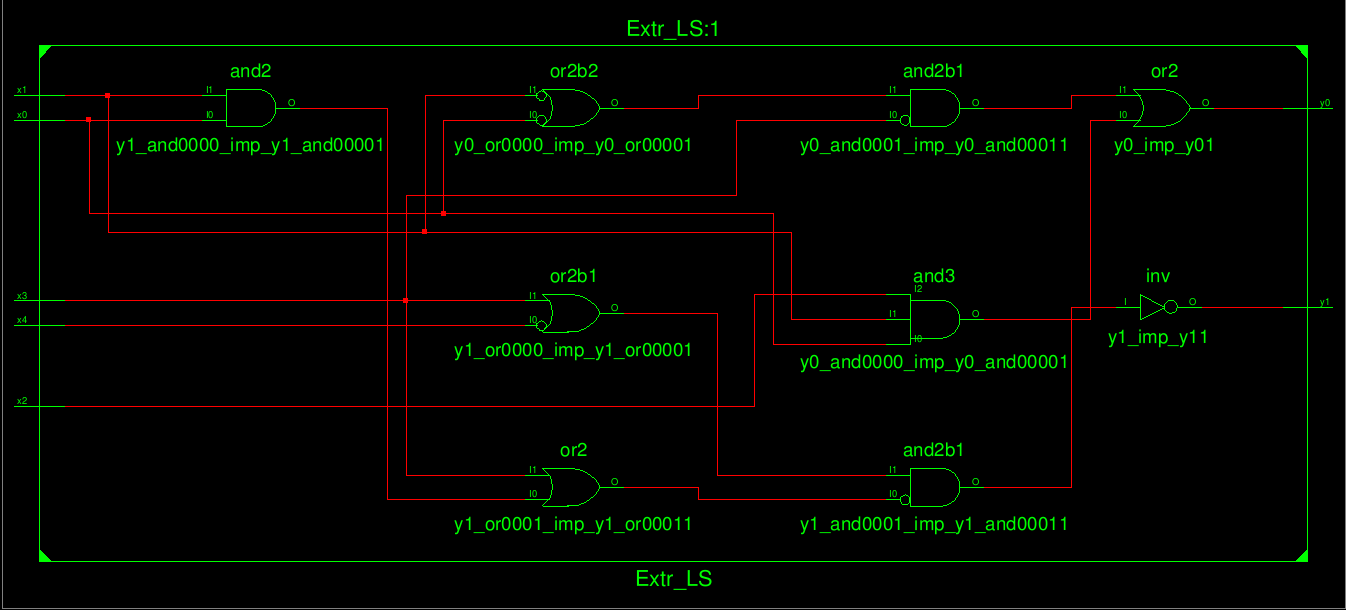

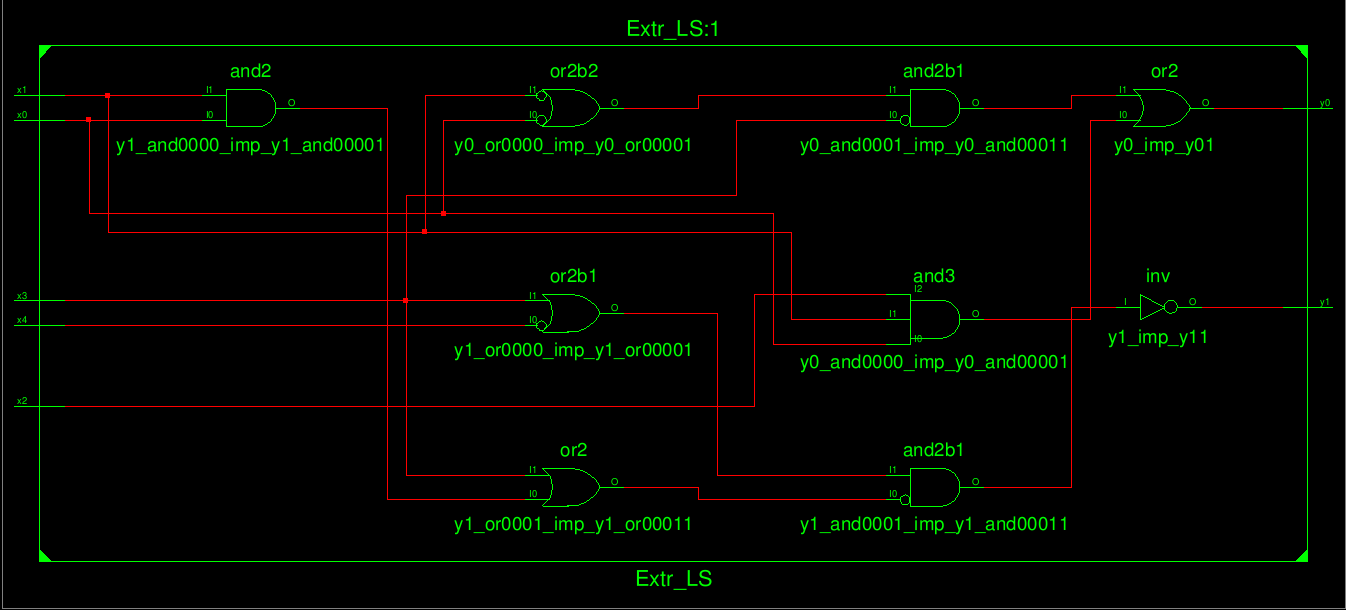

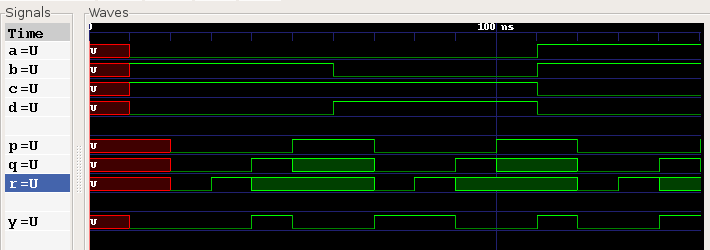

ENTRY:Extr_LS (versteckt)

Synthese und Simulation einer Gatterschaltung

Ergebnis der Register-Transfer-Synthese

Die von der Synthese extrahierte Gatterschaltung ist zwar funktionsgleich, hat aber eine Datenflussstruktur, die sich erheblich vom Berechnungsfluss unterscheidet.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Simulationsausgabe

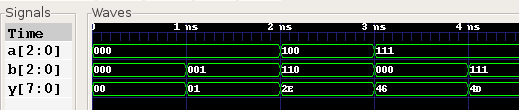

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

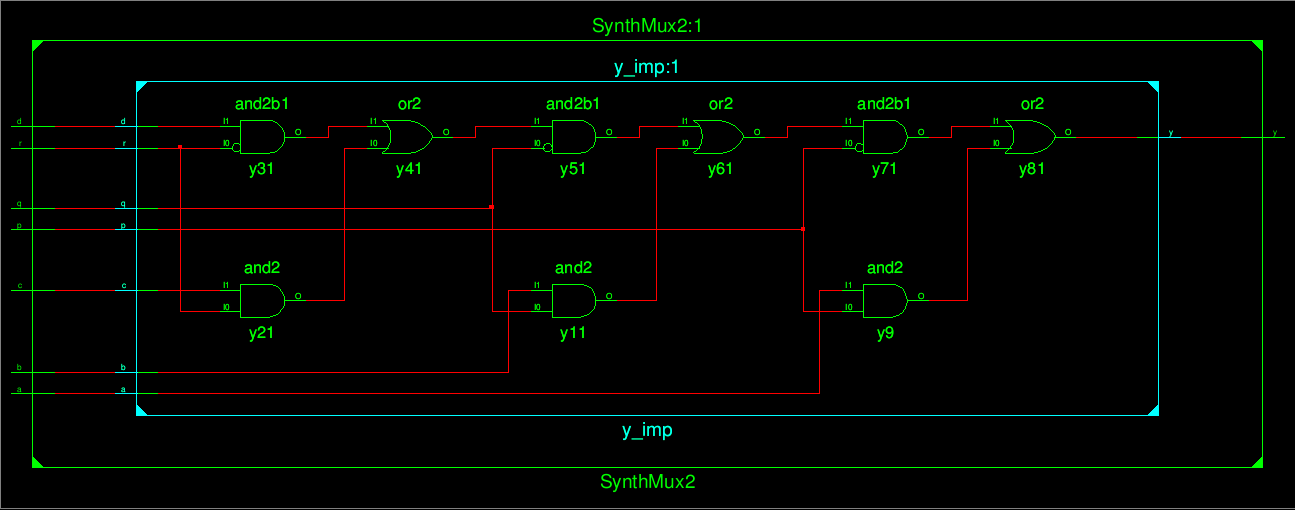

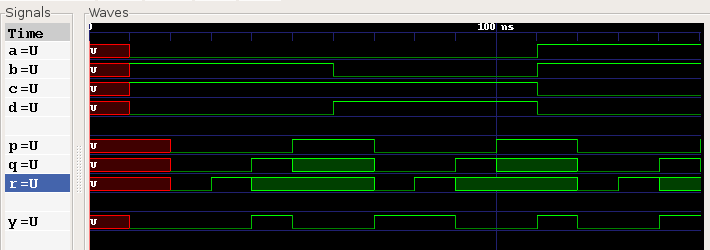

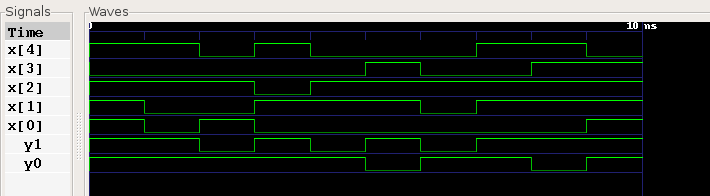

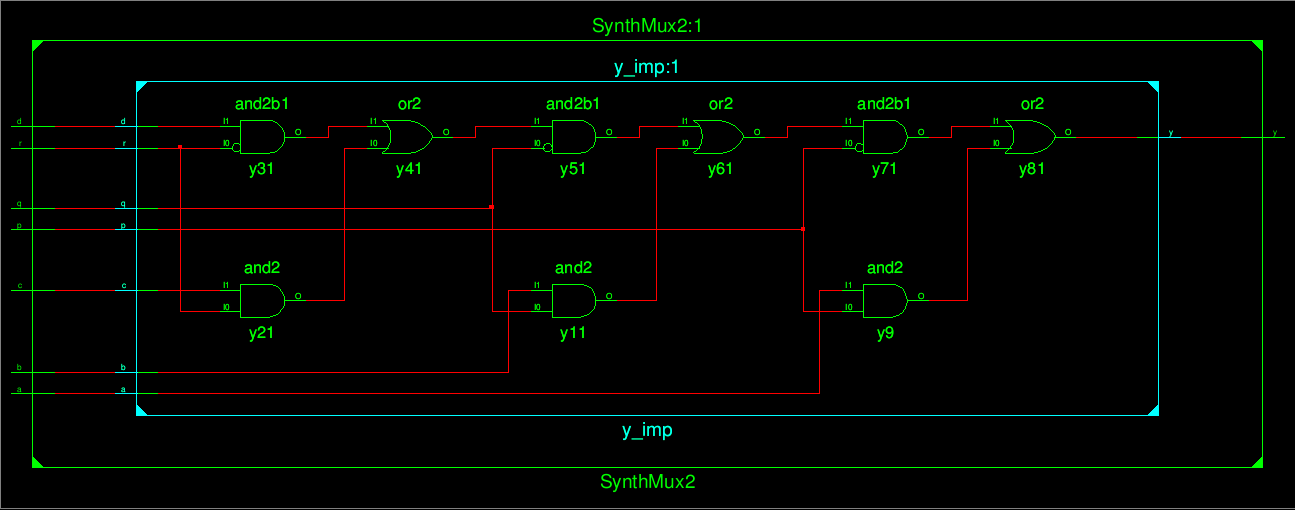

ENTRY:SynthMux2 (versteckt)

Nachbildung einer If-Elsif-Anweisung durch Multiplexer

Ergebnis der Register-Transfer-Synthese

Die drei Multiplexer, die die If-Anweisung beschreibt, werden durch je drei Gatter nachgebildet.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

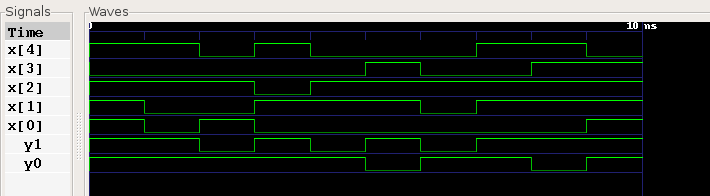

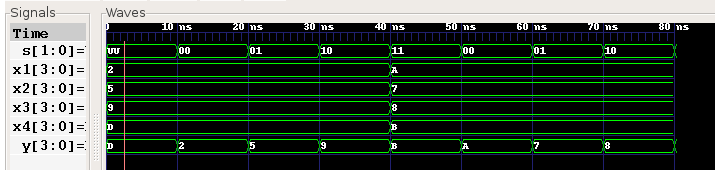

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

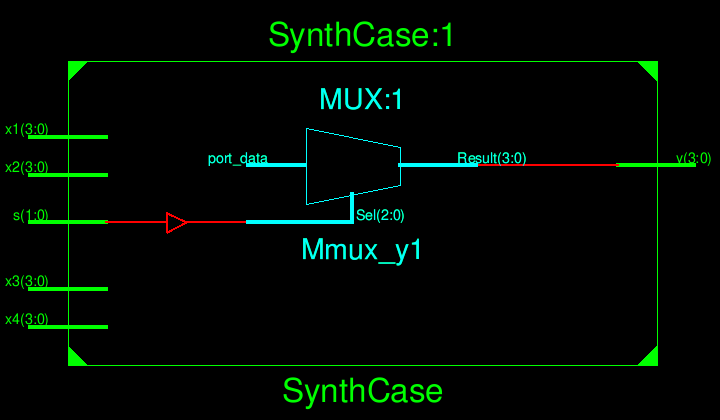

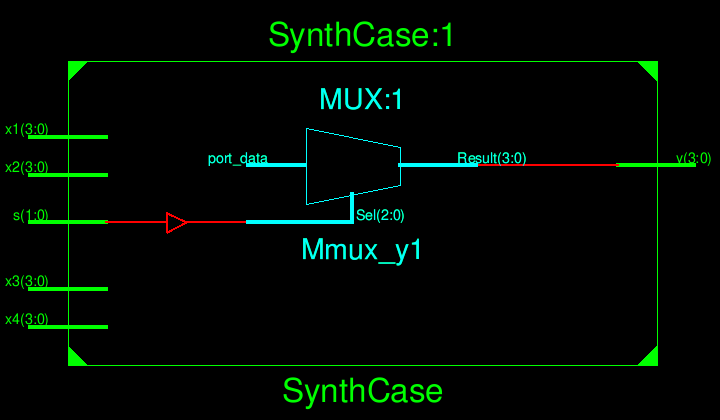

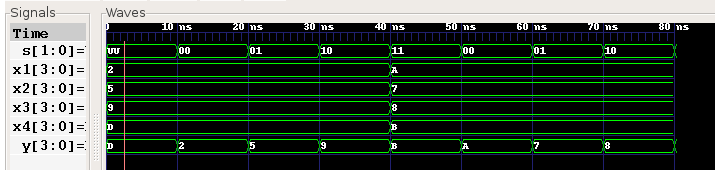

ENTRY:SynthCase (versteckt)

Nachbildung einer Auswahlanweisung durch Multiplexer

Ergebnis der Register-Transfer-Synthese

Die gesamte Case-Anweisung wird durch einen einzigen Multiplexer nachgebildet.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

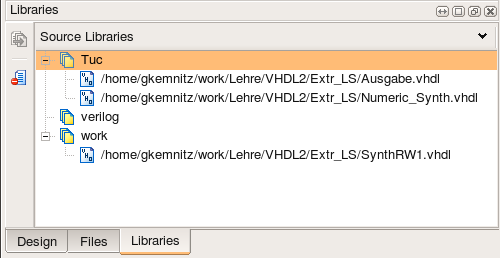

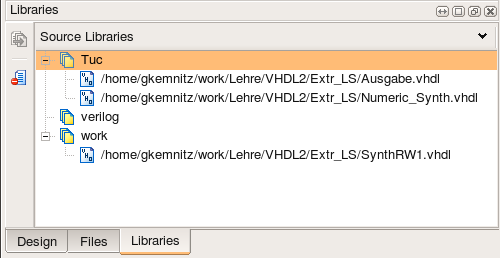

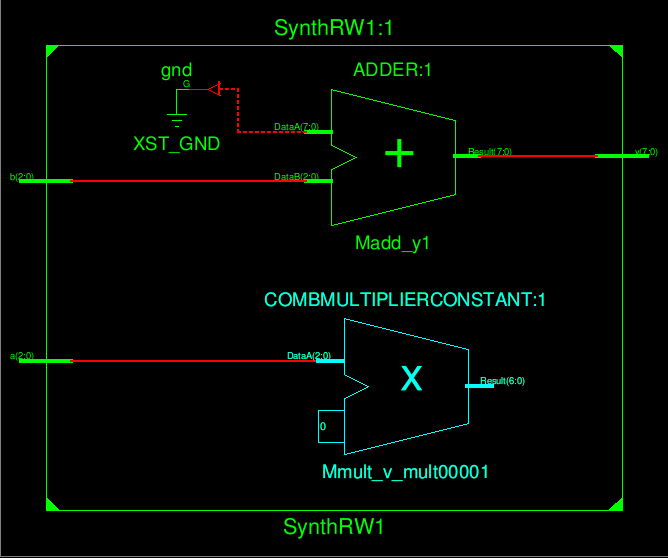

ENTRY:SynthRW1 (versteckt)

Synthesebeschreibung mit arithmetischen Operationen

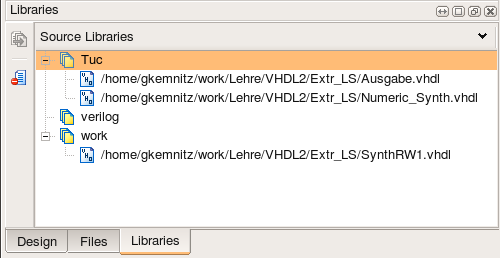

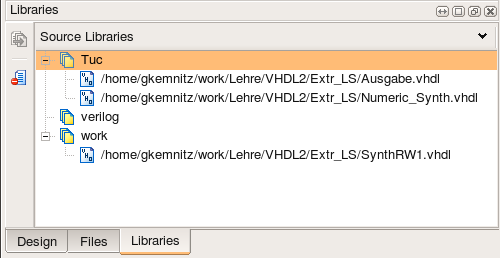

Das Beispiel verwendet die Bibliothek Tuc. Zum Anlegen der Bibliothek wird in ISE auf die Bibliotheksansicht gewechselt,

die neue Bibliothek erzeugt und in diese die genutzten Packages eingebunden. Das Fenster mit den Entwurfsquellen muss danach etwa so aussehen.

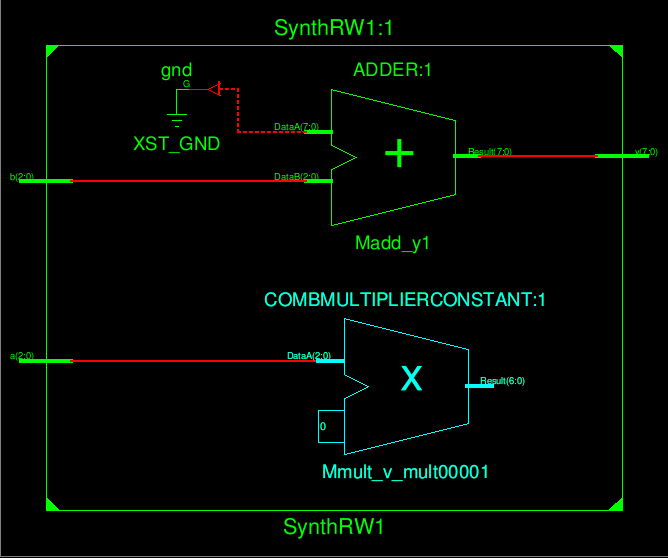

Ergebnis der Register-Transfer-Synthese

Die Multiplikation wird durch einen Multiplizierer und die Addition durch einen Addierer nachgebildet.

In dem Schaltplan, der nach der RT-Synthese angezeigt wird, fehlt die Verbindung von dem Multipliziererausgang

zu dem oberen Addierereingang, in der Schaltung ist, wie sich durch Ausprobieren der synthetisierten Schaltung zeigen lässt, diese Verbindung vorhanden.

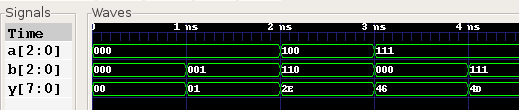

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Simulationsausgabe

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

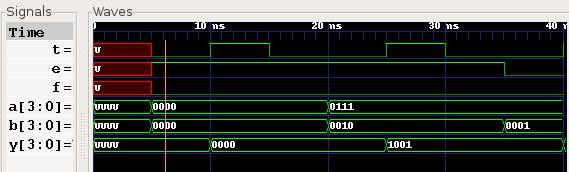

ENTRY:SynthRW2 (versteckt)

Synthesebeschreibung mit arithmetischen Operationen

Das Beispiel verwendet die Bibliothek Tuc. Zum Anlegen der Bibliothek wird in ISE auf die Bibliotheksansicht gewechselt,

die neue Bibliothek erzeugt und in diese die genutzten Packages eingebunden. Das Fenster mit den Entwurfsquellen muss danach etwa so aussehen.

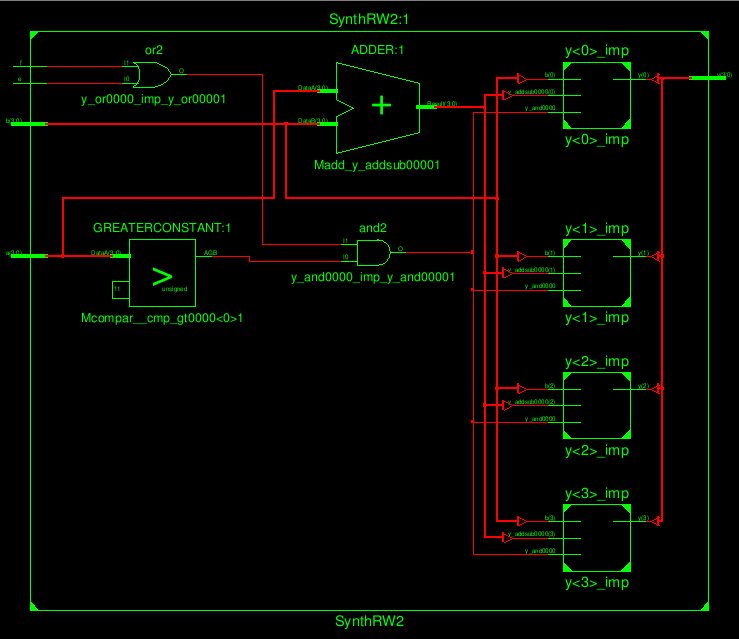

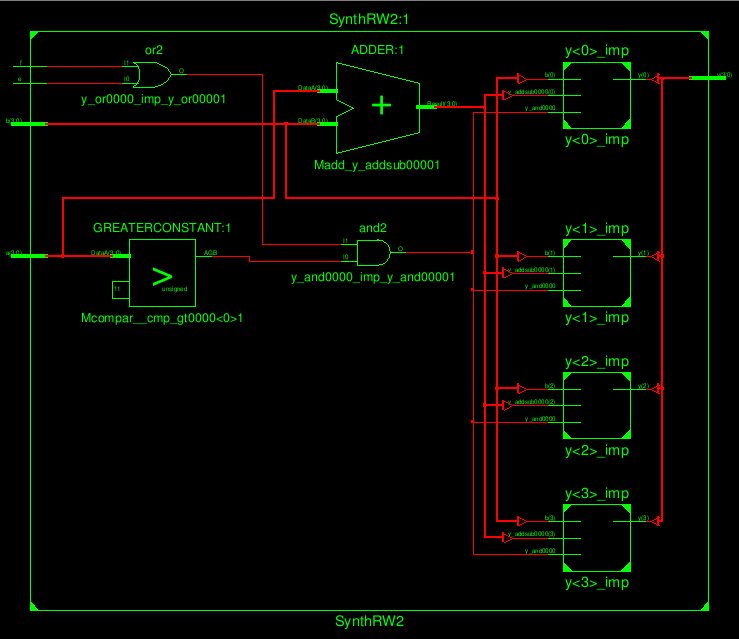

Ergebnis der Register-Transfer-Synthese

Die if-else-Anweisung wird durch die vier Schaltungsblöcke rechts im Bild, die, wenn man sich den Inhalt anzeigen lässt, jeweils einen 1-Bit-2:1-Multiplexer aus vier Gattern enthalten, nachgebildet. Aus dem Größer-Operator wird der GREATERCONSTANT-Baustein, aus der Addition der Addierer und aus der UND- und der ODER-Verknüpfung je ein Gatter.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

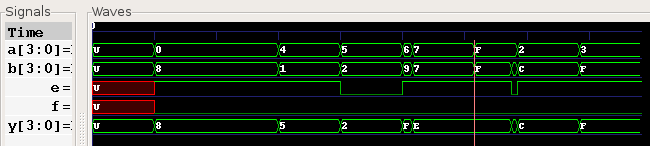

Simulationsausgabe

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

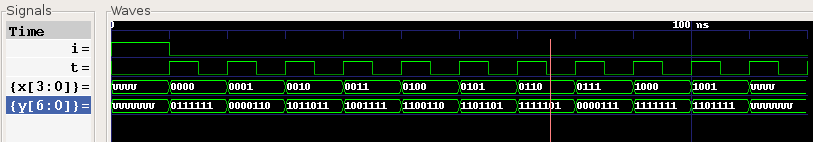

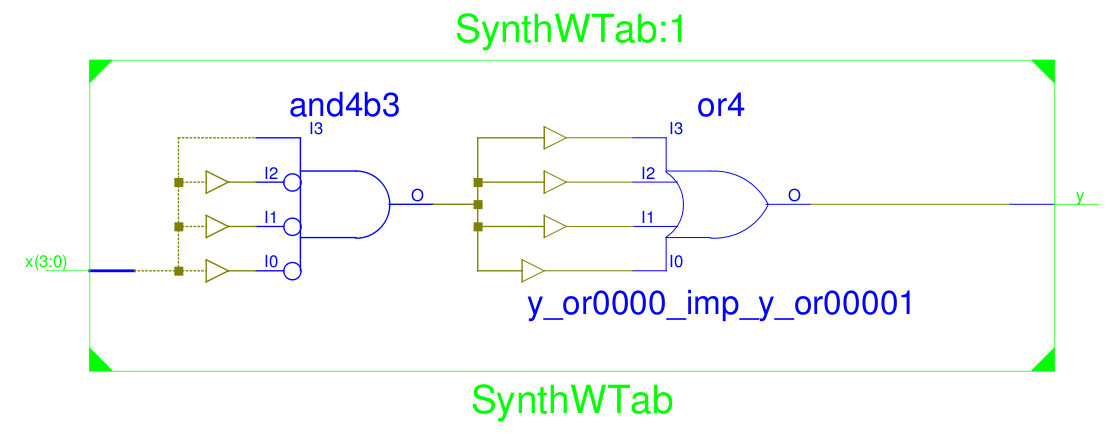

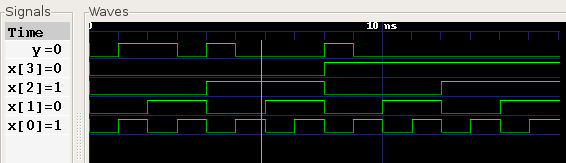

ENTRY:SynthWTab (versteckt)

Synthesbeschreibung einer Wertetabelle

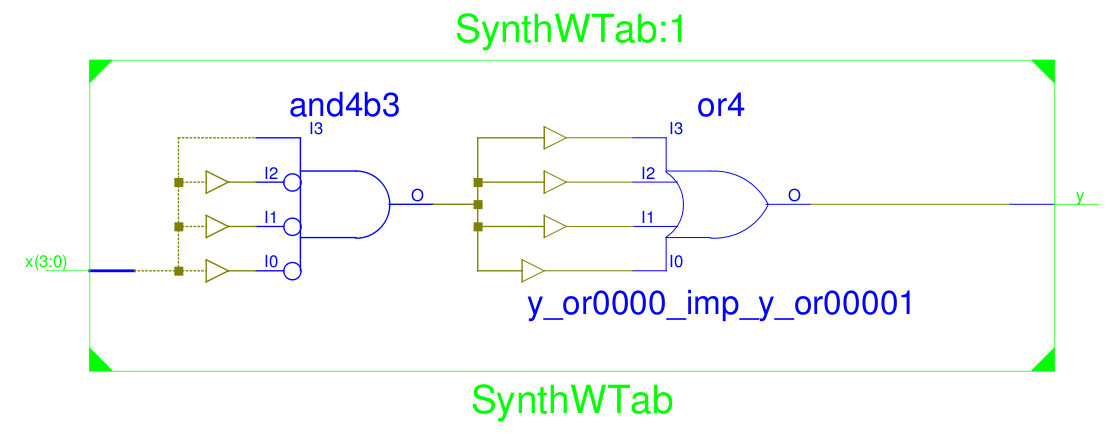

Ergebnis der Register-Transfer-Synthese

Die Schaltung wird durch eine angedeutete UND-ODER-Verknüpfung nachgebildet.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Simulationsausgabe

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

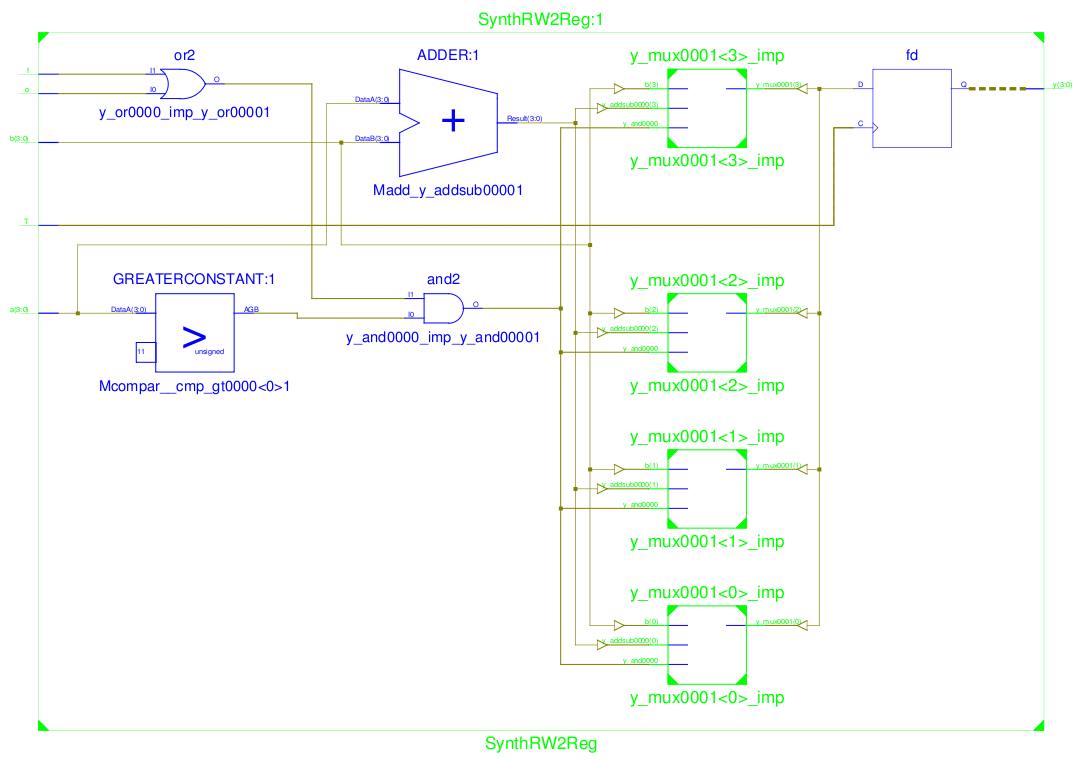

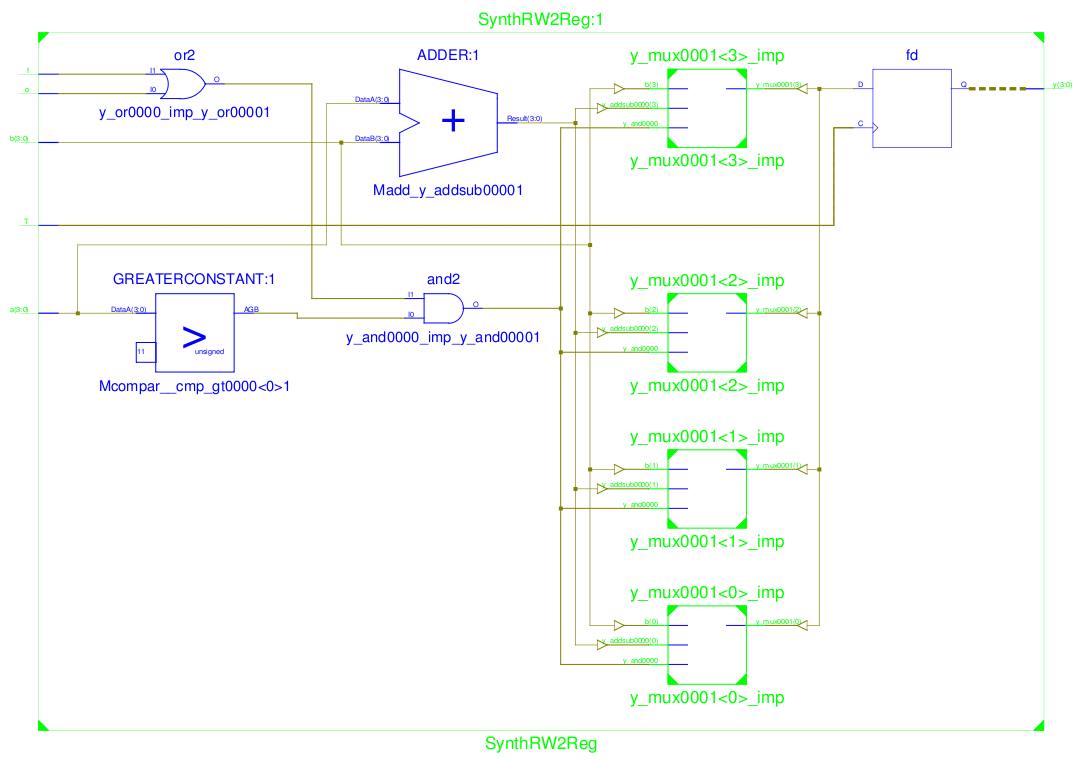

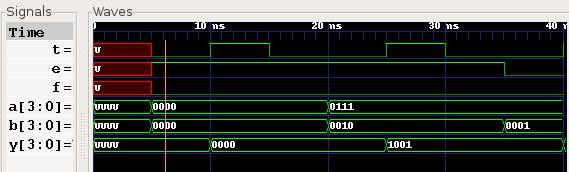

ENTRY:SynthRW2Reg (versteckt)

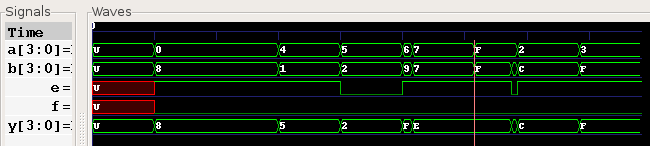

Arithmetische, logische und Vergleichoperatoren etc. plus Abtastung

Ergebnis der Register-Transfer-Synthese

Der Vergleich und die Addition sind durch Rechenwerke, die beiden logischen Operationen durch

logische Gatter, die Fallunterscheidung durch vier Multiplexer und das Abtasten durch ein

4-Bit-Register nachgebildet.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Simulationsausgabe

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

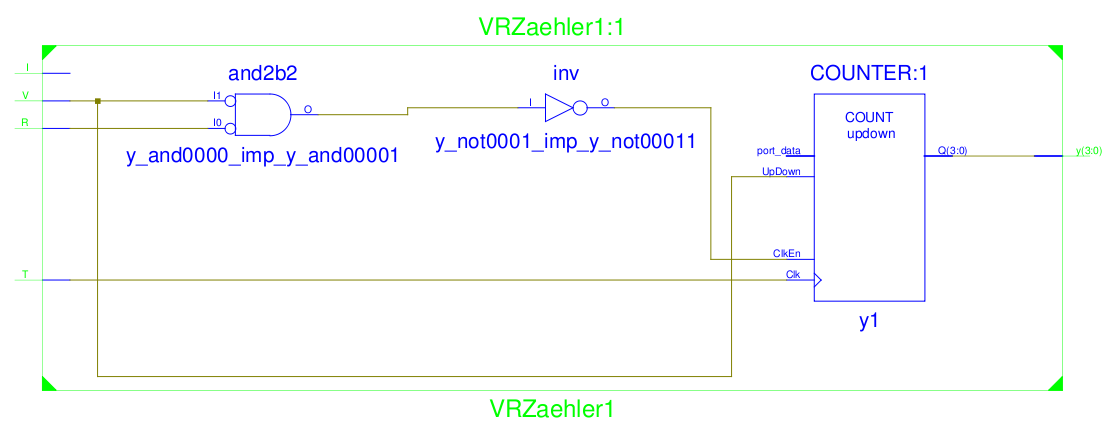

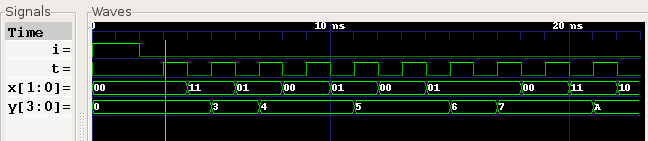

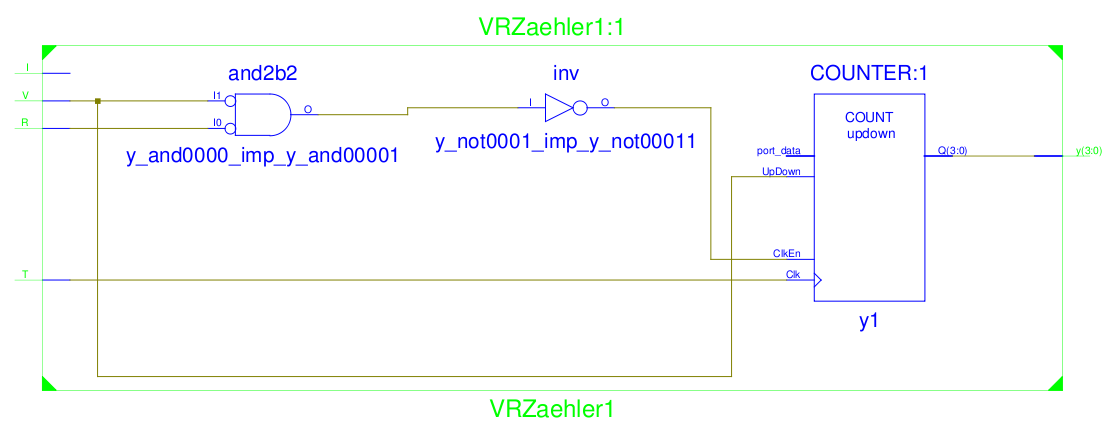

ENTRY:VRZaehler1 (versteckt)

Vorwärts-/Rückwärtszähler

Ergebnis der Register-Transfer-Synthese

Die Synthese fasst das Register und die Increment- und die Decrement-Funktion zu einem

Vorwärts-/Rückwärtszähler zusammen. Der Steuereingang für die Zählrichtung wird mit dem

Signal für Vorwärtszählen und das Freiganesignal für den Zähler praktisch mit der ODER-Verknüpfung

der beiden Zählsignale verknüpft. Das

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Simulationsausgabe

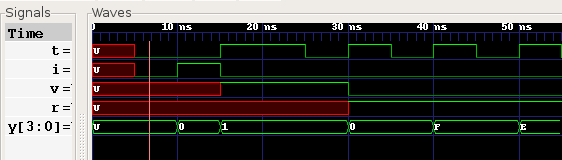

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

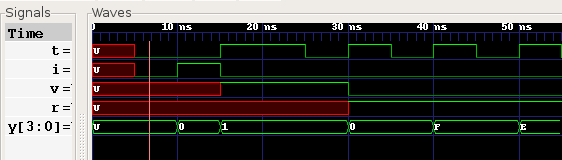

ENTRY:VRZaehler2 (versteckt)

Funktionsgleicher Vorwärts-/Rückwärtszähler mit geänderter Beschreibungsstruktur

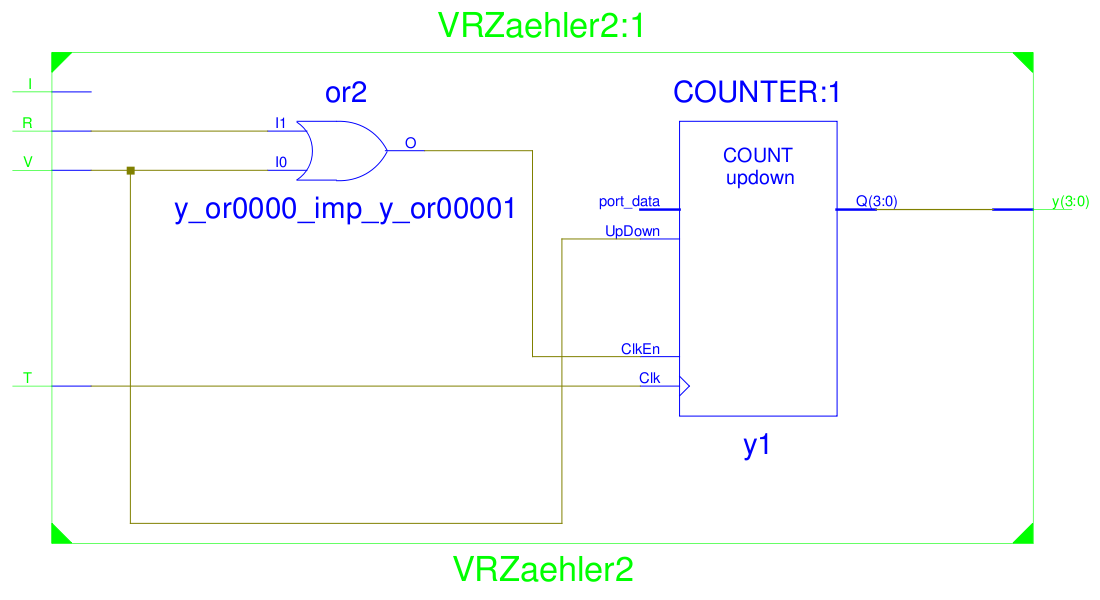

Ergebnis der Register-Transfer-Synthese

Die Synthese findet genau wie bei dem Vorwärts-/Rückwärtszähler im Beispiel zuvor

einen Zählerbaustein. Der einzige Unterschied zum Ergebnis für die funktionsgleiche Schaltung

aus dem Beispiel zuvor ist, dass die ODER-Verknüpfung nicht durch ein

UND-Gatter mit Eingabe- und Ausgabeinvertierung, sondern direkt durch ein ODER-Gatter nachgebildet wird.

|

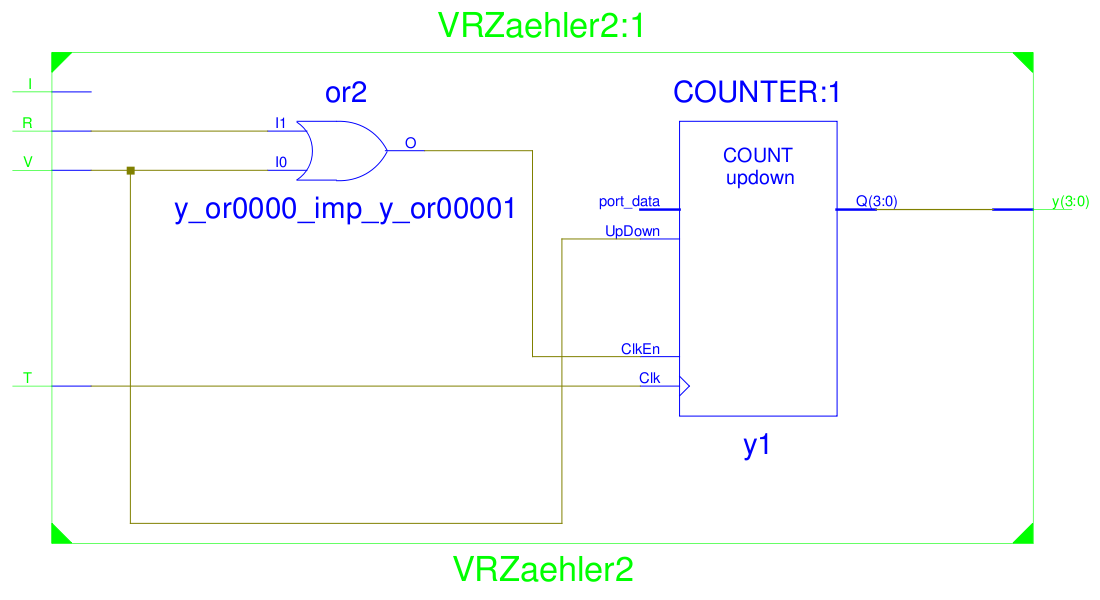

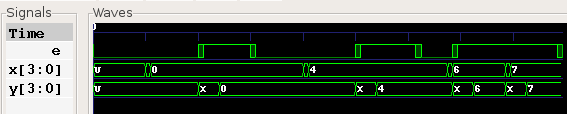

ENTRY:VarSR (versteckt)

Vorwärts-/Rückwärtszähler

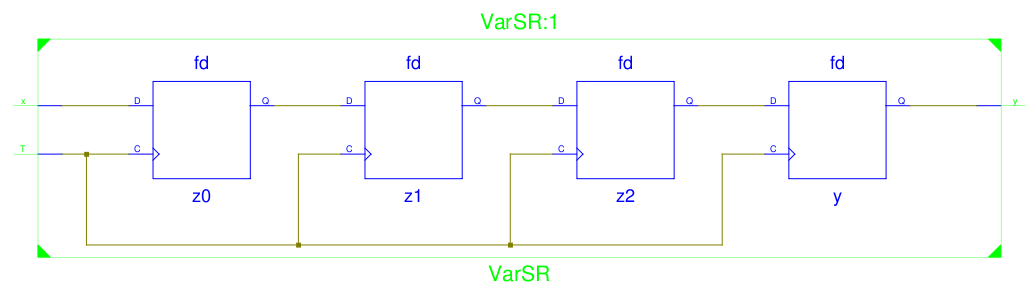

Ergebnis der Register-Transfer-Synthese

Die Beschreibung wir in ein 4-Bit-Schieberegister übersetzt.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

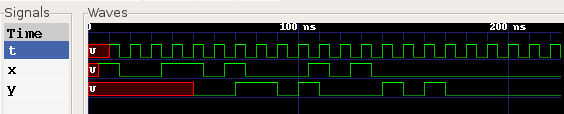

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

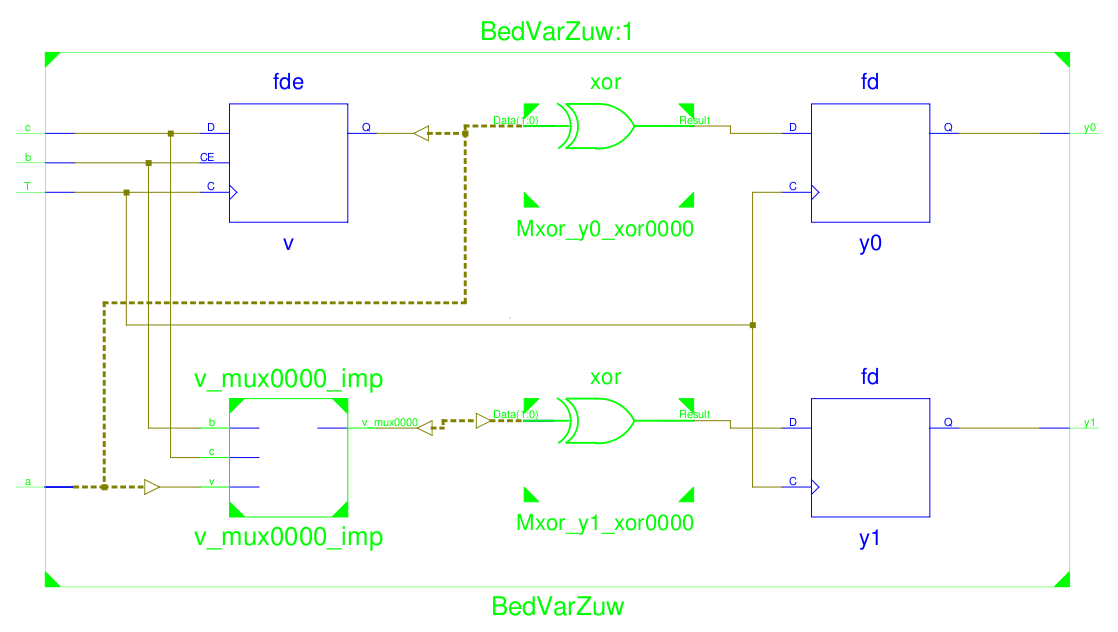

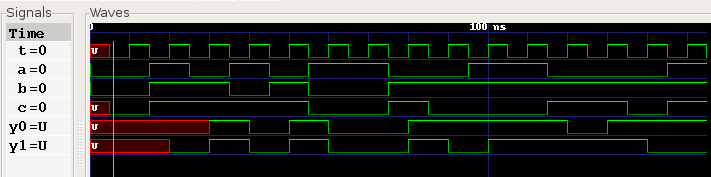

ENTRY:BedVarZuw (versteckt)

Bedingte Variablenzuweisung in einem Abtastprozess

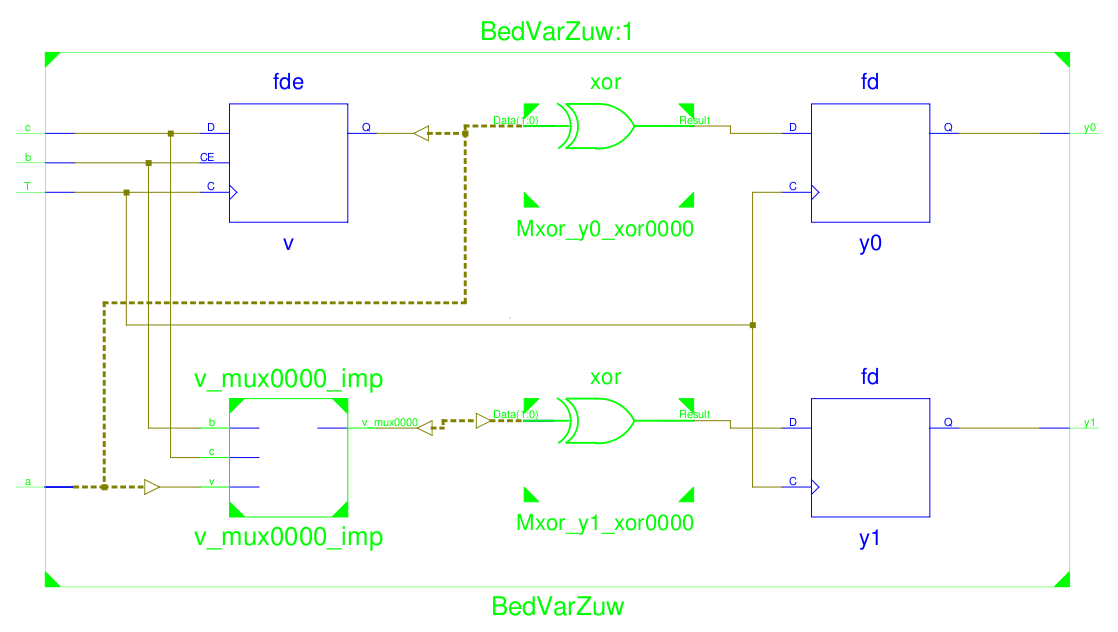

Ergebnis der Register-Transfer-Synthese

Die interne Variable, der nur bedingt ein Wert zugewiesen wird, und die beiden Ausgabesignale

werden durch Register nachgebildet. Das Register für y0 übernimmt die EXOR-Verknüpfung des gespeicherten

Variablenwertes. Die Schaltung zur Bildung des Eingabesignals für das Register von y1 besteht aus einem

Multiplexer und einem EXOR-Gatter. Die Multiplexerschaltung gibt für b=0 den Bitvektor a&c und

sonst den Bitvektor a&Q weiter.

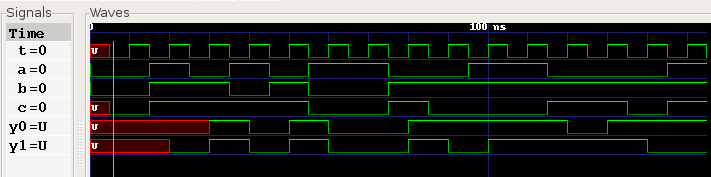

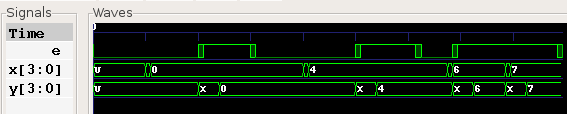

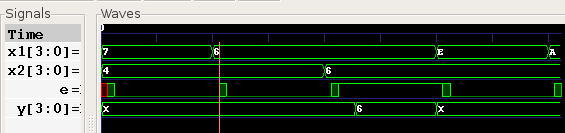

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

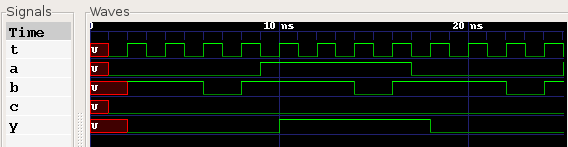

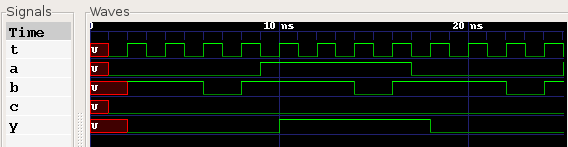

ENTRY:Latch (versteckt)

Simulationsmodell für ein Latch (Abb. 2.21)

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

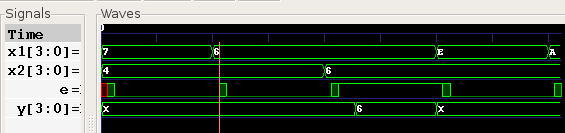

ENTRY:VglLatch (versteckt)

Simulation des Zeitverhaltens der Latch-Schaltung mit

dem Vergleicher zur Bildung des Übernahmesignals (Abb. 2.22)

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

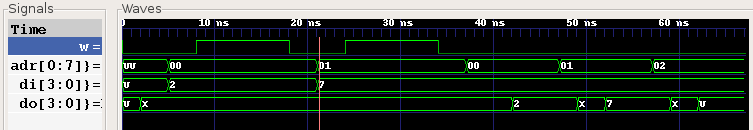

ENTRY:LatchBS (versteckt)

Blockspeicher aus vier Latches (Abb. 2.23)

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:BedVarZuwLatch (versteckt)

Abtastprozess mit einer bedingten Variablenzuweisung,

die auch mit einem Latch nachgebildet werden kann (Abb. 2.24)

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

-->

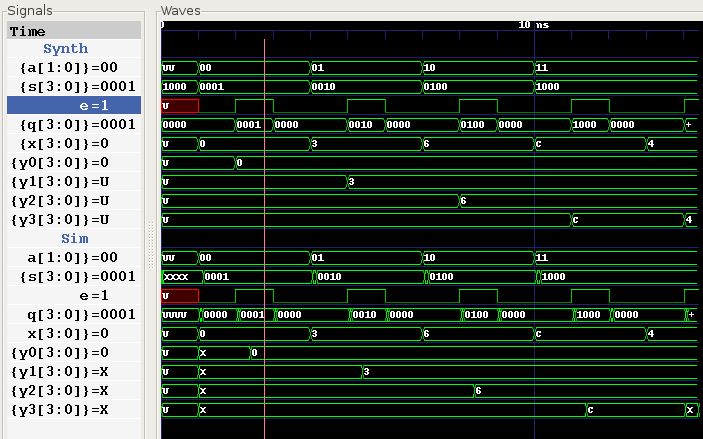

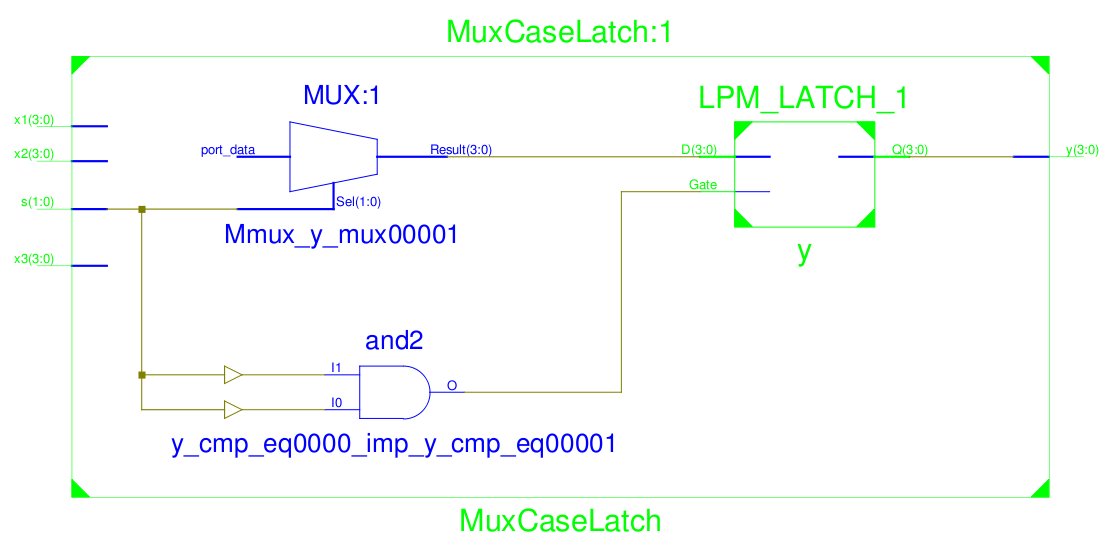

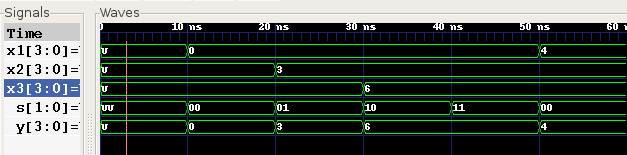

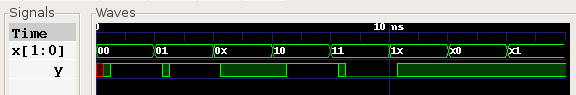

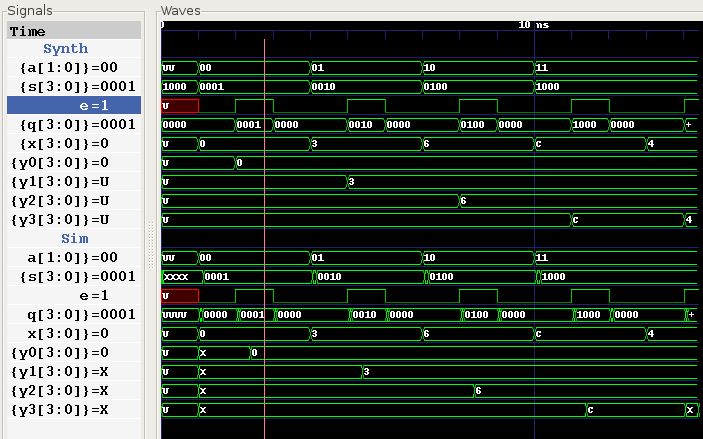

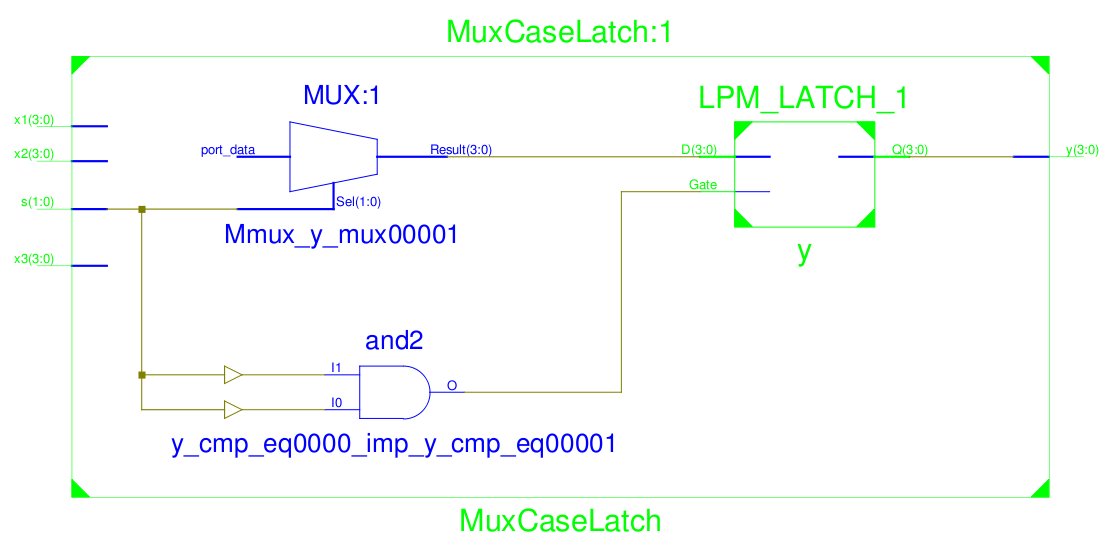

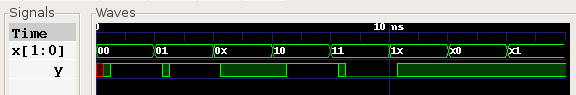

ENTRY:MuxCaseLatch (versteckt)

Unbeabsichtigtes Latch durch eine fehlende Zuweisung in einer Auswahlanweisung

Ergebnis der Register-Transfer-Synthese

Die Synthese fügt hinter dem Multiplexer ein Latch ein, das für den Auswahlwert s=11 den

den vorherigen Ausgabewert des Multiplexers speichert.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

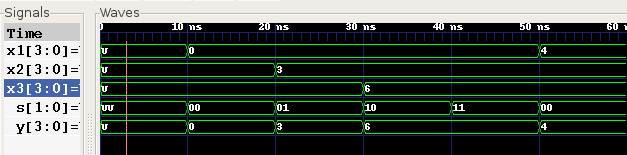

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

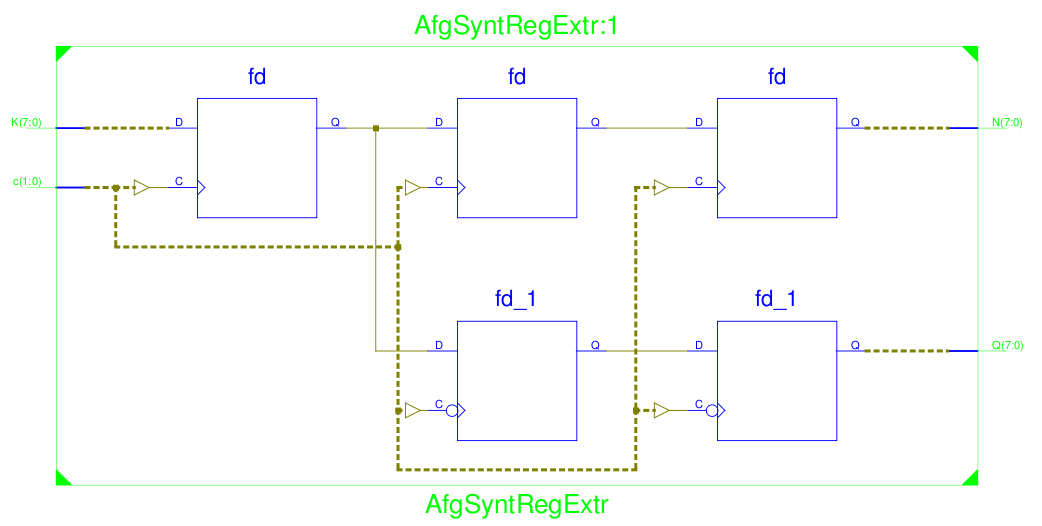

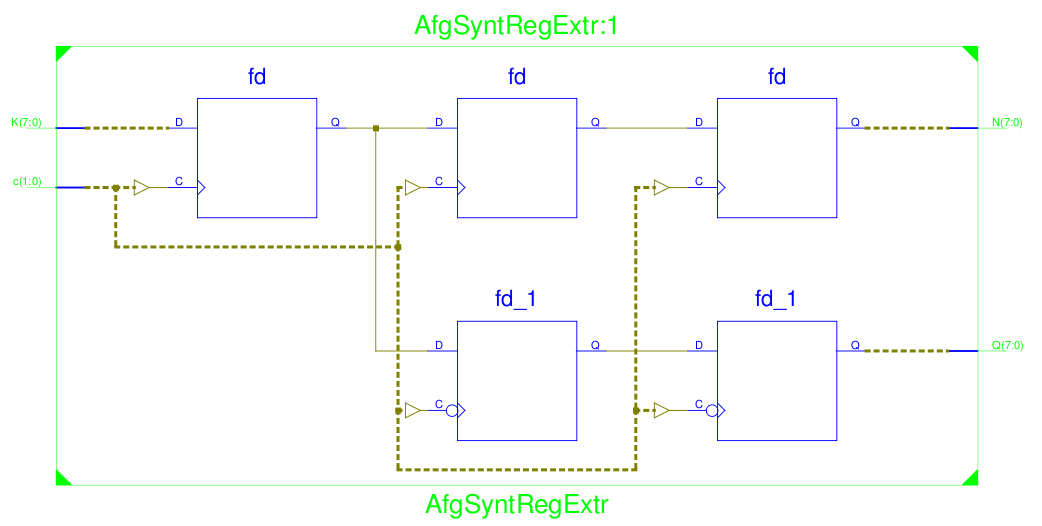

ENTRY:AfgSynthRegExtr (versteckt)

Aufgabe 2.1

Ergebnis der Register-Transfer-Synthese

Die Synthese fasst die beiden Takte zu einem Bus zusammen und extrahiert eine Schaltung aus insgesamt

fünf 8-Bit-Registern. Die Register vom Typ fd übernehmen ihre Eingabedaten mit der steigenden und

die Register vom Typ fd_1 mit der fallenden Flanke des jeweiligen Taktes.

Testrahmen

|

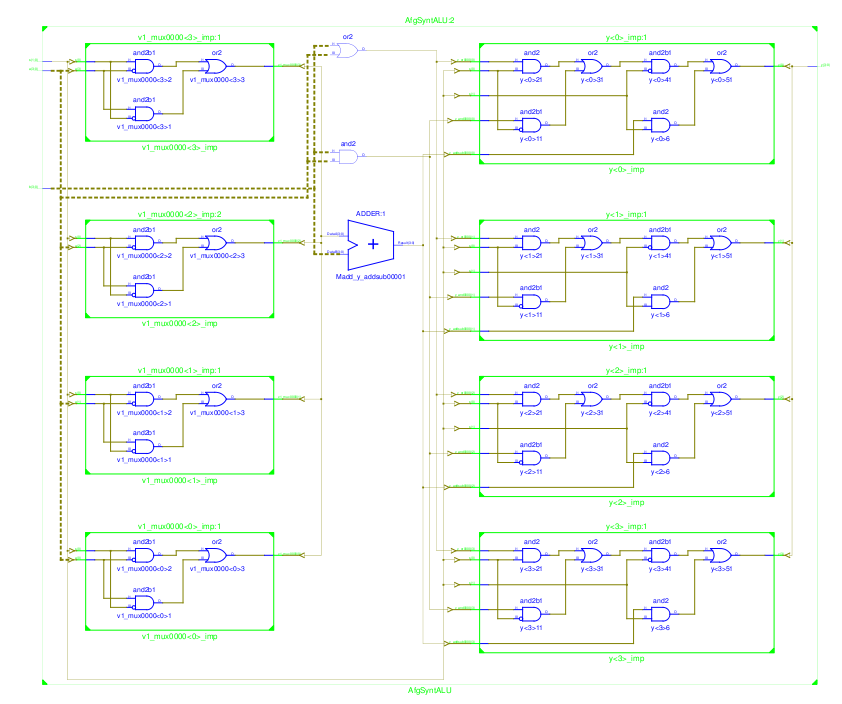

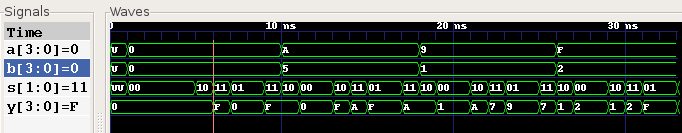

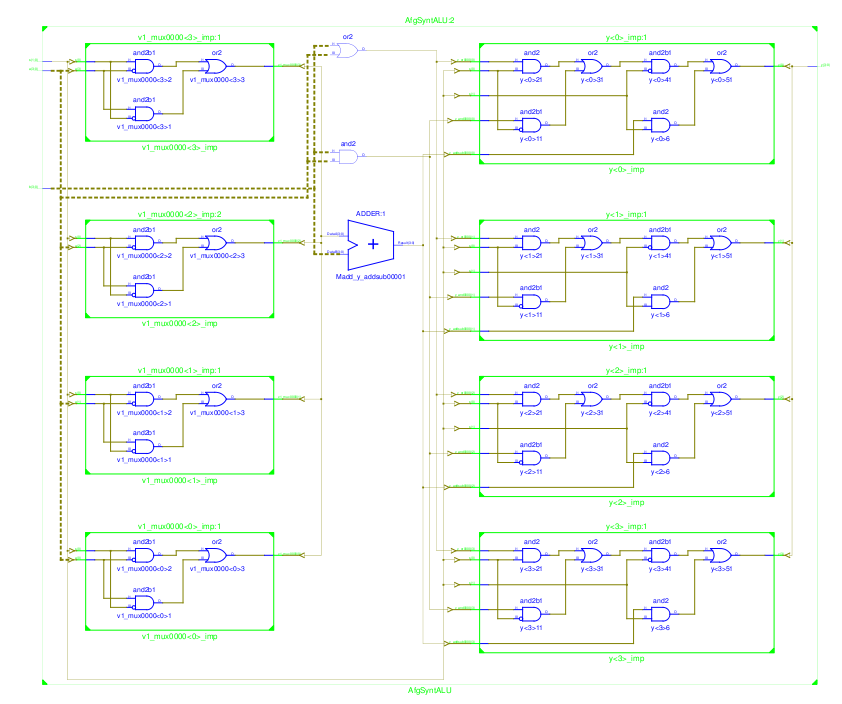

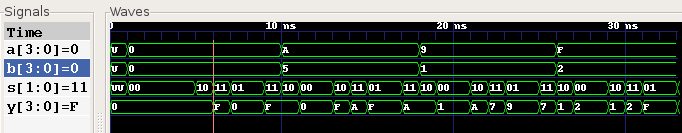

ENTRY:AfgSynthALU (versteckt)

Aufgabe 2.2

Ergebnis der Register-Transfer-Synthese

Die vier linken grünen Kästen bilden EXOR-Gatter nach und realisieren eine 4-Bit gesteuerte Negation

zur Umschaltung zwischen Addition und Subtraktion. Der Addierer, das bitweise UND und das bitweise ODER

sind jeweils zu einem Funktionsblock zusammengefasst. Die vier grünen Blöcke auf

der rechten Seite sind die 3:1-Multiplexer für die Ergebnisauswahl.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

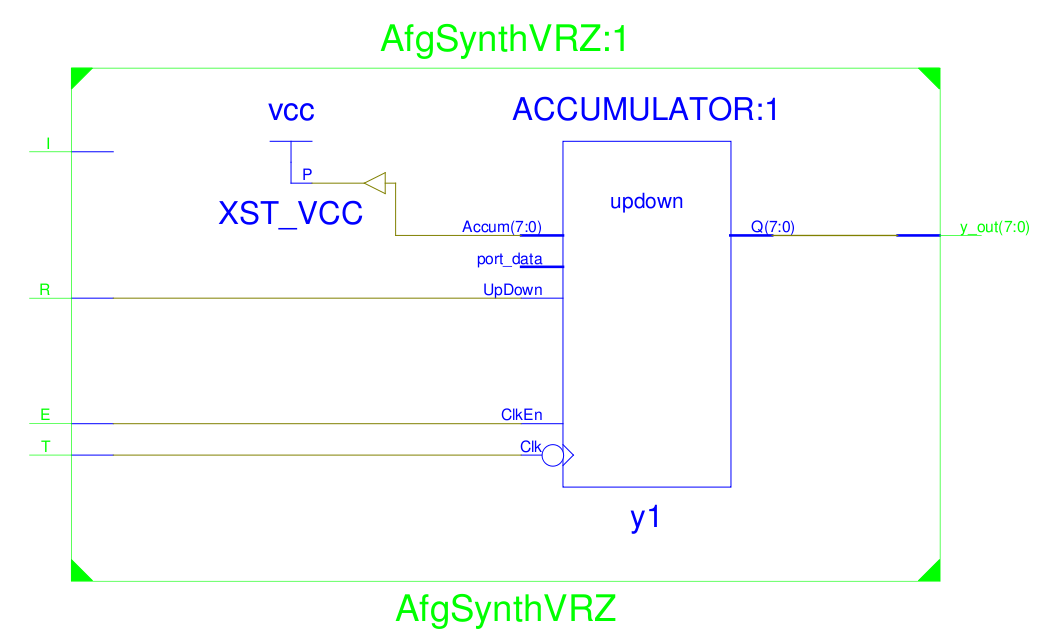

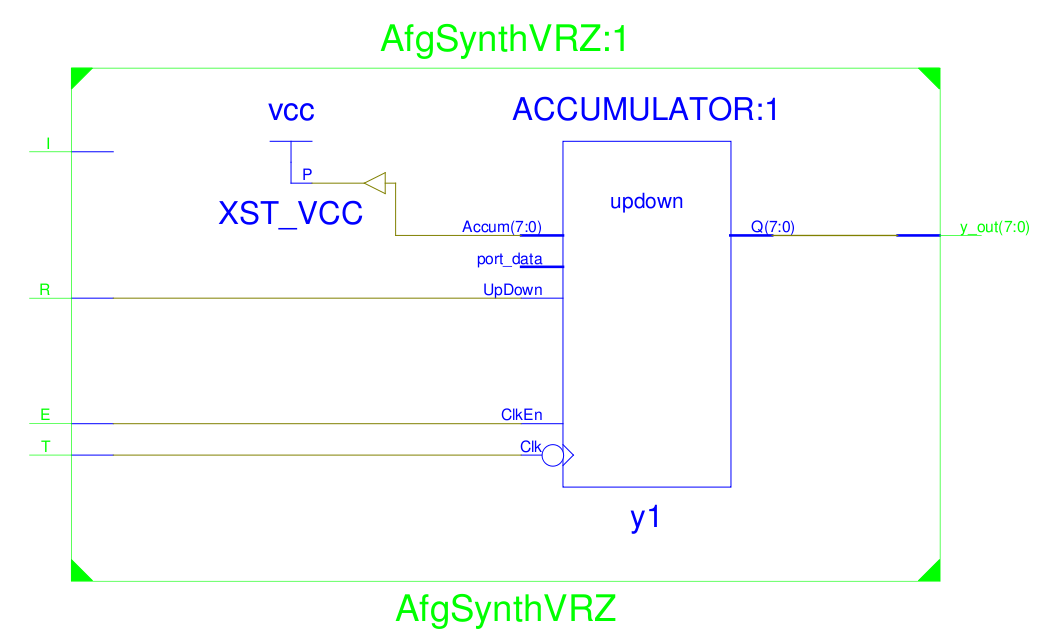

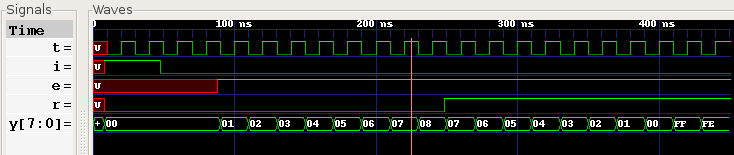

ENTRY:AfgSynthVRZ (versteckt)

Aufgabe 2.3

Ergebnis der Register-Transfer-Synthese

Für die Zielfunktion kennt das System einen geeigneten Funktionsblock.

Testrahmen

Kommados zum Übersetzen und Ausführen der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:xxxxx2 (versteckt)

2.2 Schaltungsvereinfachung auf Basis der Schaltalgebra

2.2.4 KV-Diagramm

2.2.6 Zusammenfassung und Übungsaufgaben

2.5 Addierer

2.5.1 Ripple-Addierer

- Iterative Beschreibung eines Ripple-Addierers (Abb. 2.81):

[RippleAdd.vhdl]

2.5.2 Serieller Addierer

2.5.4 Hierarchischer Addierer

2.6 Weitere Rechenwerke

2.6.5 Dividierer

2.6.9 Zusammenfassung und Übungsaufgaben

|

2.1 Register-Transfer-Synthese

Die Synthese erfolgt mit dem Entwurfssystem ISE in folgenden Schritten:

- Neues Projekt anlegen

- VHDL-Datei mit "Add Source" einbinden

- Wenn verwendet, die Bibliothek Tuc anlegen und mit "Add Source" die genutzten Packages einbinden

- Unter "Processes" "Synthesize - XST" und Entwurfsziel

"View RTL Schematic" auswählen und Synthese starten

Um nicht für jedes Beispiel, ein neues Projekt anlegen und die Tuc-Bibliothek neu erzeugen

zu müssen, genügt es, die VHDL-Datei im Projekt auszutauschen und die Synthese neu zu starten.

Eine detailliertere Anleitung enthält die Praktikumsanleitung des ersten [

VHDL-Praktikums.

2.1.2 Kombinatorische Schaltungen

2.1.3 Kombinatorische Schaltungen mit Abtastregistern

2.1.4 Latches

2.1.6 Entwurfsfehler und Fehlervermeidung

2.1.7 Zusammenfassung und Übungsaufgaben

2.2 Schaltungsvereinfachung auf Basis der Schaltalgebra

2.2.4 KV-Diagramm

2.2.6 Zusammenfassung und Übungsaufgaben

2.5 Addierer

2.5.1 Ripple-Addierer

- Iterative Beschreibung eines Ripple-Addierers (Abb. 2.81):

[RippleAdd.vhdl]

2.5.2 Serieller Addierer

2.5.4 Hierarchischer Addierer

2.6 Weitere Rechenwerke

2.6.5 Dividierer

2.6.9 Zusammenfassung und Übungsaufgaben

ENTRY:DialogAdd (versteckt)

Testrahmen für einen dialogorientierten Test einer 4-Bit-Addition

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Betrag (versteckt)

Test eine Fallunterscheidung zur Betragsbildung

Hilfe zum Übersetzen und Ausführen

|

ENTRY:WTab (versteckt)

Test eine Auswahlanweisung zur Nachbildung einer Wertetabelle

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestWhile (versteckt)

Test einer While-Schleife

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestFor (versteckt)

For-Schleife über den Indexbereich eines Bitvektors

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_fWtab (versteckt)

Package mit der zu testendenen kombinatorischen Beispielfunktion

Testrahmen für einen dialogorientierten Test

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_countx (versteckt)

Package mit der zu testendenen kombinatorischen Beispielfunktion

Testrahmen für einen dialogorientierten Test

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestRand (versteckt)

Package mit der "unreinen" Funktion rand zur Bereistellung von Zufallszahlen

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestW5T (versteckt)

Package mit der zu testenden Prozedur

Testrahmen

Hilfe zum Übersetzen und Ausführen

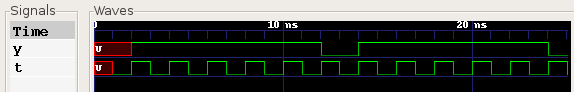

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:TestNLProz (versteckt)

Beschreibung des Testobjekts, der Testeingabebereitstellung und der

der Protokollierung der Testergebnisse durch nebenläufige Prozeduren

Testrahmen

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:Test_Lsg3_1 (versteckt)

Lösung zu Aufgabe 3.1

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Lsg3_2 (versteckt)

Package UP_pack

Package Rand_pack

Lösungs-Package

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Lsg3_3 (versteckt)

Package UP_pack

Package Rand_pack

Lösungs-Package

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Lsg3_4 (versteckt)

Package UP_pack

Package Rand_pack

Lösungs-Package

Testrahmen

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:TestApfel (versteckt)

Testrahmen zu Beispiel 3.2 (Typenverträglichkeit)

Hilfe zum Übersetzen und Ausführen

|

ENTRY:SkalAttr (versteckt)

Testrahmen zu Beispiel 3.4 (skalare Attribute)

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Feld (versteckt)

Testrahmen zu Beispiel 3.5 (Feldattribute)

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestZL (versteckt)

Testrahmen zu Beispiel 3.5 (Feldattribute)

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Afg_Typenvertraegl (versteckt)

Aufgabe 3.5

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Afg_ZB_Enum (versteckt)

Aufgabe 3.6

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Afg_tZustand3SG (versteckt)

Aufgabe 3.9

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Afg3_10 (versteckt)

Package zu Aufgabe 3.10

Testrahmen zu Aufgabe 3.10

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Afg3_11 (versteckt)

Package zu Aufgabe 3.11

Testrahmen zu Aufgabe 3.11

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Afg3_12 (versteckt)

Package zu Aufgabe 3.12

Testrahmen zu Aufgabe 3.12

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_Afg3_13 (versteckt)

Package zu Aufgabe 3.13

Testrahmen zu Aufgabe 3.13

Daten zu Aufgabe 3.13

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_PEncFkt (versteckt)

Package mit der Prioritätsencoderfunktion

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:Test_MemOOP (versteckt)

objektorientiertes RAM-Modell

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

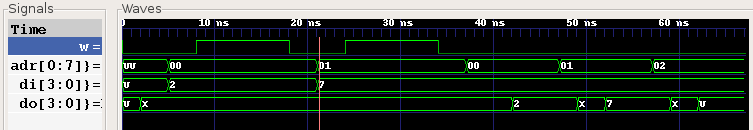

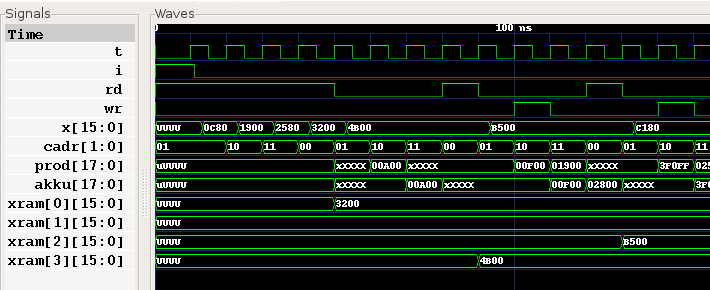

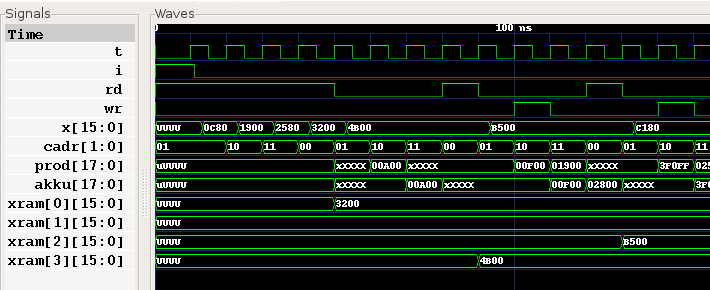

ENTRY:Test_RAM (versteckt)

Kernfunktion eines Schreib-Lese-Speichers als Prozedur

Testrahmen

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:Test_ROM (versteckt)

Initialisierungsfunktion für nur lesbare Blockspeicher

Testrahmen

Hilfe zum Übersetzen und Ausführen

Initialisierungsdaten

|

ENTRY:Test_FIFO (versteckt)

objektorientiertes FIFO-Modell

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

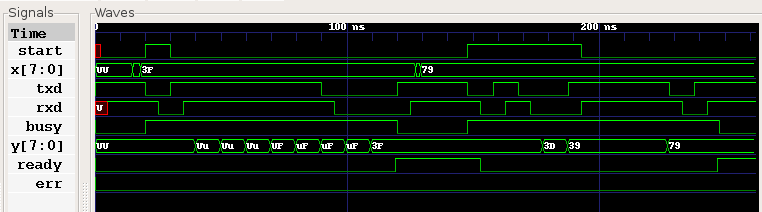

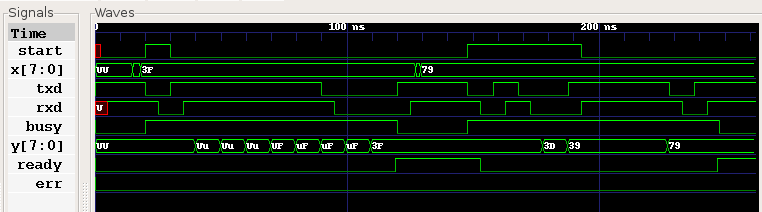

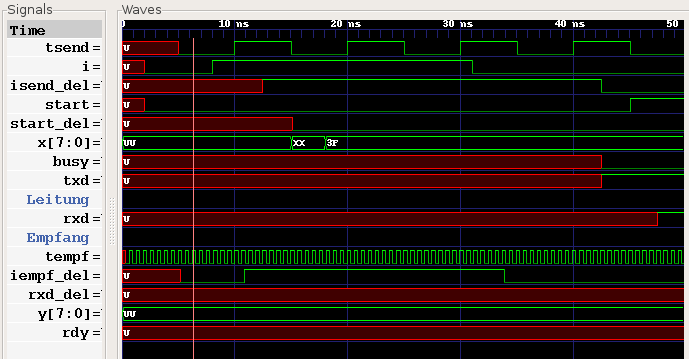

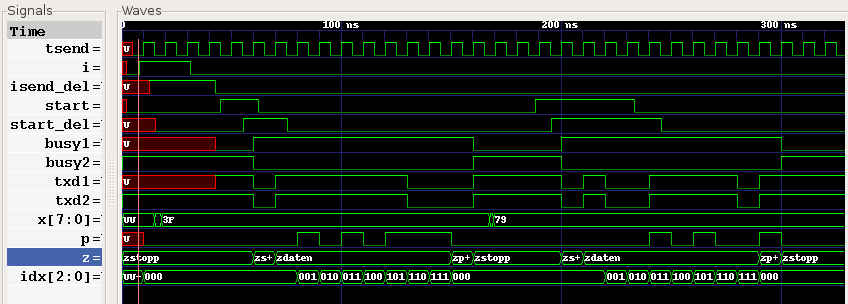

ENTRY:TestUART1 (versteckt)

ablauforientierte Beschreibung mit Wartezeiten

Testrahmen

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

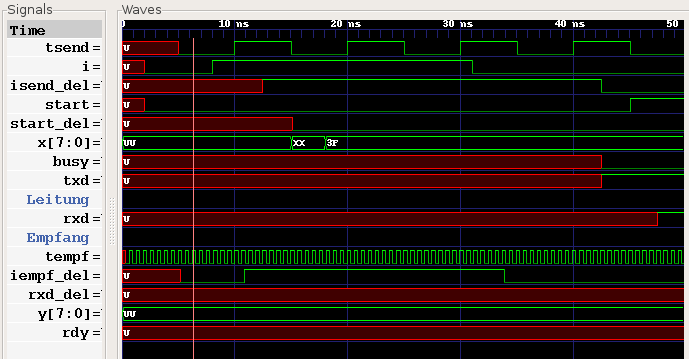

ENTRY:TestUART2 (versteckt)

ablauforientierte taktsynchronen Beschreibung

Testrahmen

Hilfe zum Übersetzen und Ausführen

Textausgabe der Signale

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

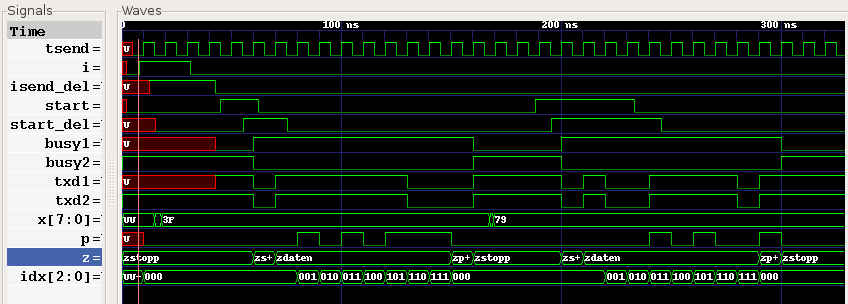

ENTRY:TestUART3 (versteckt)

ablauforientierte taktsynchronen Beschreibung

Testrahmen

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

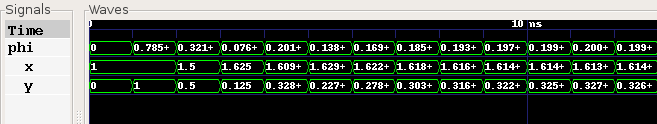

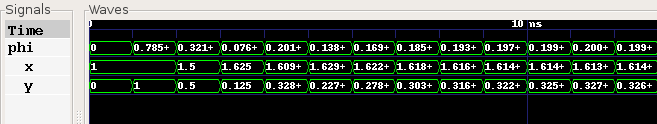

ENTRY:cordic1 (versteckt)

Verhaltensmodell zur Kontrolle des Algorithmus

Testrahmen

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:cordic2 (versteckt)

Verhaltensmodell mit einem Festkommaformat für die Wertedarstellung

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:cordic3 (versteckt)

Verhaltensmodell mit Festkommazahlen und seqentieller Multiplikation

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestAfgCount1 (versteckt)

Aufgabe 3.14

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

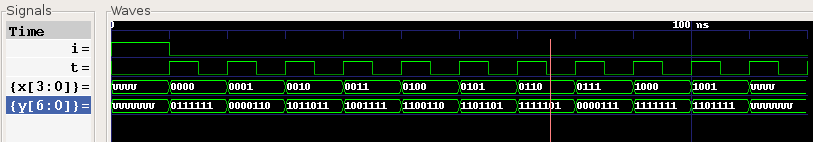

ENTRY:MVTestSeg7 (versteckt)

Package für einen Pseudo-Zufallstest mit Mehrversionsvergleich

Zwei Beschreibungsversionen des 7-Segment-Decoders

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:SollIstTest (versteckt)

Package für den Test mit Eingangen und Soll-Ausgaben aus einer Datei

Beschreibungsversionen des 7-Segment-Decoders

Testrahmen

Testeingaben und Sollausgaben

Hilfe zum Übersetzen und Ausführen

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:SpecTest (versteckt)

Package für einen Spezifikationstest für die Steuerung einer Fussgängerampel

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

ENTRY:TestGenSin (versteckt)

Aufgabe 3.18 (Sinusgenerator)

Testrahmen

Hilfe zum Übersetzen und Ausführen

|

3.1 Imperative Beschreibungsmittel

3.1.2 Fallunterscheidungen

3.1.3 Schleifen

3.1.4 Funktionen

3.1.5 Unreine Funktionen und globale Variablen

3.1.7 Prozeduren

3.1.8 Nebenläufige Prozeduraufrufe

3.1.9 Zusammenfassung und Übungsaufgaben

3.2 Anwendungsspezifische Datentypen

3.2.1 Zahlentypen

Testrahmen zu Beispiel 3.2 (Typenverträglichkeit)

3.2.4 Attribute von elementaren Datentypen

3.2.5 Felder

3.2.6 Zuordnungslisten für Feldelemente

3.2.9 Zusammenfassung und Übungsaufgaben

3.3 Ein- und Ausgabe

3.3.4 Zusammenfassung und Übungsaufgaben

3.4 Beschreibungsschablonen für digitale Schaltungen

3.4.1 Auslagerung kombinatorischer Funktionen in Packages

3.4.3 Blockspeicher

3.4.4 Ein objektorientiertes FIFO-Modell

3.4.5 Schrittweise Modellentwicklung -- Beispiel UART

3.4.6 Entwicklung eines CORDIC-Rechenwerks

ENTRY:ExportCordic

3.4.7 Zusammenfassung und Übungsaufgaben

3.5 Funktionsbausteine für den Testrahmen

3.5.1 Pseudo-Zufallstest und Mehrversionsvergleich

3.5.2 Vorab berechnete Eingaben und Soll-Werte

3.5.3 Spezifikationstest

3.5.4 Zusammenfassung und Übungsaufgaben

4.1 Entwurf und Modellierung von CMOS-Gattern

4.1.3 Signale mit mehreren Quellen und der Typ std_logic

4.1.9 Zusammenfassung und Übungsaufgaben

4.2 Zeitverhalten

4.2.1 Zeitdiskrete Simulation

4.2.5 Simulation mit geschalteten Transistorbreiten

4.3 Speicherzellen, Latches und Register

4.3.6 Taktversorgung

4.4 Schreib-Lese-Speicher

4.4.1 SRAM

4.4.3 Assoziativspeicher

ENTRY:Test_FIR1 (versteckt)

Erstes Simulationsmodell für einen FIR-Filter

Hilfe zum Übersetzen und Ausführen

Textausgaben während der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:Test_FIR2 (versteckt)

Ersatz der Zahlentypen des FIR-Filters durch Bitvektoren und Ein- und

Ausgabe über Signale

Hilfe zum Übersetzen und Ausführen

Textausgaben während der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

ENTRY:POI_pack (versteckt)

Points-of-Interest-Berechnung

|

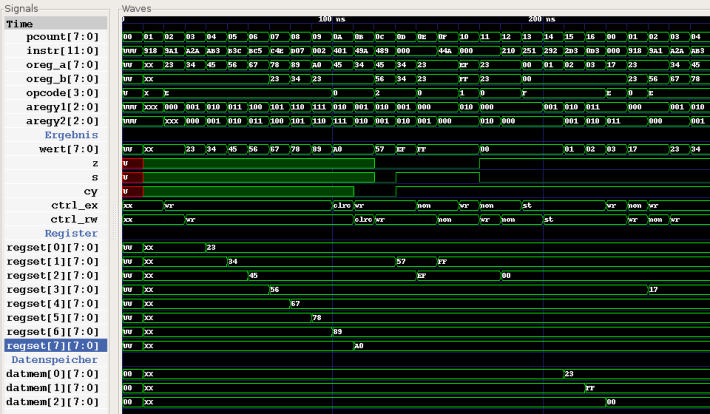

ENTRY:Test_ALU (versteckt)

Test des Rechenwerks

Hilfe zum Übersetzen und Ausführen

Textausgaben während der Simulation

|

ENTRY:Test_Sprungbedingung (versteckt)

Test der Funktion zur Prüfung Sprungbedingungen

Hilfe zum Übersetzen und Ausführen

Textausgaben während der Simulation

|

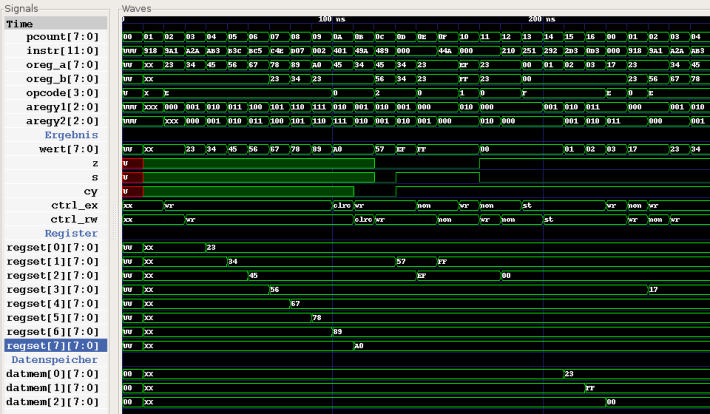

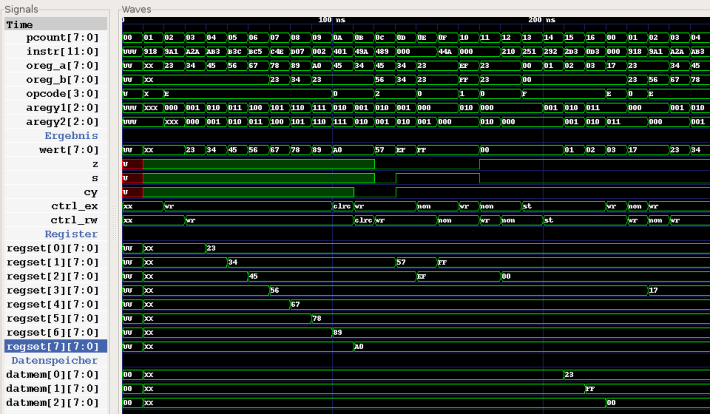

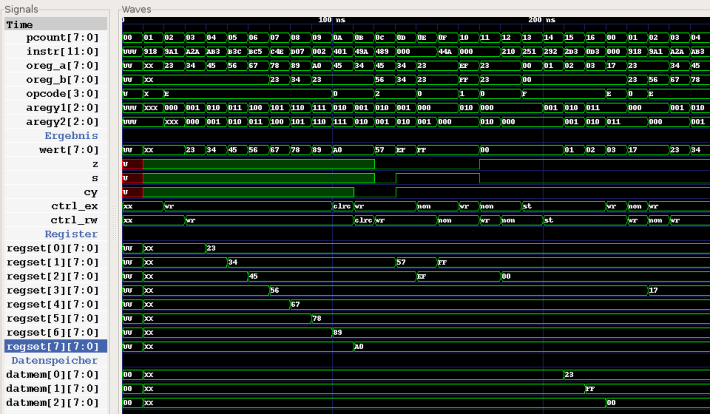

ENTRY:Test_RISC (versteckt)

Test des gesamten Funtionsmodells des RISC-Prozessors

Hilfe zum Übersetzen und Ausführen

Textausgaben während der Simulation

Signalverläufe mit GTKWAVE und der Sav-Datei aus dem Archiv

|

5.2 FIR-Filter mit Blockspeichern

5.3 Points-of-Interest-Berechnung

5.4 Entwurf eines RISC-Prozessors

1.3.5 Zusammenfassung und Übungsaufgaben

1.4 Register

1.4.6 Zusammenfassung und Übungsaufgaben

1.5.5 Zusammenfassung und Übungsaufgaben

1.6.7 Zusammenfassung und Übungsaufgaben

Autor: gkemnitz, Letzte Änderung: 09.04.2024 17:10:43