Lehre.PraktSP_2016 (Struktur)

Praktikum Softprozessor

|

(G. Kemnitz)

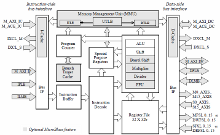

Programierbare Logikschaltkreise (FPGA) können inzwischen Schaltungen aufnehmen, die in herkömmlicher Schaltungstechnik aus Millionen von Logikgattern bestehen. Da passt ein komplettes maßgeschneidertes Rechnersystem hinein ... |

|

Versuchsobjekt sind Xilinx-FPGA-Baugruppen NEXYS3. Der Rechner wird aus vorentworfenen Rechnerbausteinen (Prozessor, Speicher-Controller,

Speichern, Ein-/Ausgabeschnittstellen etc.) und

optional auch selbst entworfenen Digitalschaltungen zusammengesetzt. Aus der Konfigurationsbeschreibung wird zum einen eine VHDL-Beschreibung

für die Synthese und werden zum anderen die Header, und Treiber etc. für den Software-Entwurf generiert. Die Programmierung erfolgt in C

in einer speziell konfigurierten Eclipse-Umgebung.

Zielgruppe: BA Technische Informatik und Interessenten Credits: (ECTS): 3 |

Schritt-für-Schritt-Anleitungen

| Nr. | Anleitung | Inhalt | Ergänzungsmaterial |

|---|---|---|---|

| 1 | [MinSys] | Eintwicklung und Test eines minimalen Rechnersystems | [main.c] [nexys3.ucf] |

| 2 | [Debug] | Arbeit mit dem Debugger | [system_bd.bmm] [system.bit] [system.xml] |

| 3 | [Chipscope] | Hardware-Test mit Chipscope | [cst_main.c] [system_bd.bmm] [min_sys.mhs] [min_sys.ucf] [system.bit] [system.xml] |

| 4 | [LMB-IO] | Systemsentwurf mit dem LMB-IO-Modul | [system.ucf] [system_bd.bmm] [test_pit.c] [test_seg7.c] [system.mhs] [test_fit.c] [test_uart.c] [system.bit] [system.xml] |

| 5 | [LMB-LA] | Test des LMB-IO-Systems mit ChipScope | [system.ucf] [system_ohne_ILA.mhs] [system_mit_ILA.mhs] |

| 6 | [Interrupt] (in Arbeit) | Nutzung von Interrupts | [system.ucf] [sys_interrupt.mhs] [polling_test.c] [interrupt_test.c] [sys_interrupt.ucf] |

| 7 | [HS-CoDesign] (in Arbeit) | Integration eigener Hardware-Bausteine | [system.ucf] |

Aufgaben

[A1] [A2] [A3]Doku

[MicroBlaze Processor Reference Guide]Prüfung und Bewertung

Es sind die ersten fünf Schritt-für-Schritt-Anleitungen und alle drei Aufgabenblätter abzuarbeiten. Die Leistungsüberprüfung erfolgt stichprobenhaft, wenn alle Aufgaben gelöst sind. Bis zur Leistungsüberprüfung sind alle Entwurfsdaten aufzubewahren. Eine Anmeldung im Prüfungsamt ist nicht erforderlich. Vor der Leistungsüberprüfung ist zu klären, ob eine benoteter oder ein unbenoteter Leistungsnachweis benötigt wird. Während der Leistungsüberprüfung dürfen Sie alle Unterlagen und Ausarbeitungen nutzen.Autor: gkemnitz, Letzte Änderung: 06.11.2024 20:33:30

TU Clausthal 2020 Impressum