# Schritt-für-Schritt-Anleitung für den Entwurf und Test eines Minimalsystems (SP-SFS-1)

Prof. G. Kemnitz, TU Clausthal, Institut für Informatik

22. Februar 2018

#### Zusammenfassung

In dieser Schritt-für-Schritt-Anleitung wird mit EDK ein minimales Rechnersystem konfiguriert, die erforderlichen Datein für die Programmierung der Rechnerhardware in den Logikschaltkreis und die Programmeintwicklung erzeugt. Dann wird SDK gestartet, die Projektumgebung eingerichtet, ein kleines Programm zum Ausprobieren der Hardware erstellt und mit diesem der entworfene Rechner ausprobiert.

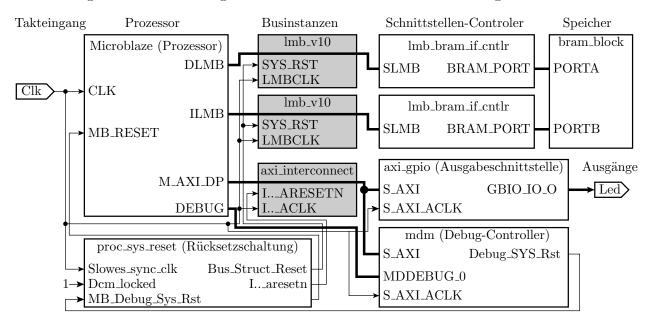

## 1 Das zu entwerfende System

Abb. 1 zeigt die Blockstruktur des zu entwerfenden Rechnersystems. Es besteht aus dem Prozessor, einem über lokale Speicherbusse (LMB's) und entsprechende Controller angeschlossenen Dualport-Speicher für die Befehle und Daten, einer über den AXI-Bus angeschlossene Ausgabgeschnittstelle für die Ansteuerung der Leuchtdioden auf der Baugruppe, einem über den AXI-Bus angeschlossenen Debug-Controller und einer Rücksetzschaltung.

Abbildung 1: Das zu entwerfende Rechnersystem

### 2 Hardware-Entwurf

Der System Builder von EDK ist in der Lage, das System fast vollständig zu konfigurieren. Der Rest ist manuell nachzubessern. Abb. 2 zeigt die Programmoberfläche von EDK und die

auszuwählende Schaltfläche »New BSP-Project« für den Start des System Builders.

Abbildung 2: Startoberfläche von EDK

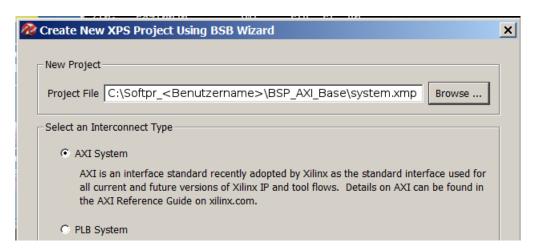

In dem sich öffnenden Fenster, Abb. 3, ist die Projektdatei und »AXI-System« auszuwählen. Für jedes neue Projekt sollte ein eigenes Verzeichnis angelegt werden, was auch innerhalb des Menüs möglich ist<sup>1</sup>. Die nicht gezeigten Auswahlfenster in der Abbildung darunter bleiben leer. Weiter mit »Ok«.

Abbildung 3: Festlegung des Arbeitsverzeichnisses und der Art des Bussystems

Im nächsten Fenster, Abb. 4, sind auszuwählen:

- »Create a System for a Custom Board« (Wir haben keines der auswählbaren Boards),

- der Typ des zu programmierenden Logikschaltkreises (spartan6, xc6slx16, ..),

- die Taktfrequenz 100 MHz, die Art des Rücksetzsignals (high-aktiv).

Für die nicht gezeigten Eintragsfelder sind die vorgegebenen Werte beizubehalten. Weiter mit  $Next \ll 1$

<sup>&</sup>lt;sup>1</sup>Arbeiten Sie direkt auf Laufwerk C (statt auf einem Netzlaufwerk oder einem Stick) und sichern Sie sich am Ende die wichtigen Dateien. Wenn Sie ein Netzlaufwerk verwenden, verlängert sich die Übersetzungszeit um einige Minuten.

| E. | Base System Builder AXI flow                                                                           |

|----|--------------------------------------------------------------------------------------------------------|

|    | Board                                                                                                  |

|    | C Create a System for the Following Development Board (Pre-selected Device Info)                       |

|    | Board Vendor Xilinx    Board Name Kintex-7 KC705 Evaluation Platform    Board Revision C               |

|    |                                                                                                        |

|    | Board Configuration                                                                                    |

|    | Architecture spartan6 ▼ Device xc6slx16 ▼ Reference Clock Frequency 100.00                             |

|    | Package                                                                                                |

|    | - Select a System                                                                                      |

|    | Single MicroBlaze Processor System System Information                                                  |

|    | Dual MicroBlaze Processor System  This system consists of one instance of MicroBlaze with external mem |

|    |                                                                                                        |

Abbildung 4: Auswahl des Systemtyps und des programmierbaren Logikschaltkreises

Im nächsten Fenster Abb. 5 wird die Blockspeichergröße festgelegt, kann eine Gleitkommarecheneinheit (FPU) und können periphere Einheiten wie Speichercontroller, Timer, und Schnittstellenschaltungen hinzugefügt werden. Unser Minimalsystem soll nur eine Ausgabeschnittstelle für die acht Led's auf der Baugruppe erhalten. Das Hinzufügen erfolgt über »Add Device«. Die weiterhin erforderlichen Bausteine (Debug-Controller, Prozessor, ...) werden ohne explizite Auswahl eingefügt.

| ocessor Frequency 100 MHz       |                                                                           |      |             |            |

|---------------------------------|---------------------------------------------------------------------------|------|-------------|------------|

| rocessor Configuration          |                                                                           |      |             |            |

| Select a Processor microblaze_0 | Enable Floating Point Unit<br>Local Memory Size<br>Instruction Cache Size | 8 KB |             | ▼<br>▼     |

| elect and Configure Peripherals | Data Cache Size                                                           | 8 KB |             | <u></u>    |

| Available Peripherals           | <br>Included Peripherals for microblaz                                    | e_0  |             | Select All |

|                                 |                                                                           |      | Parameter   |            |

| Add Device Export Import        | Core                                                                      |      | raiailietei |            |

Abbildung 5: Konfiguration des Systems

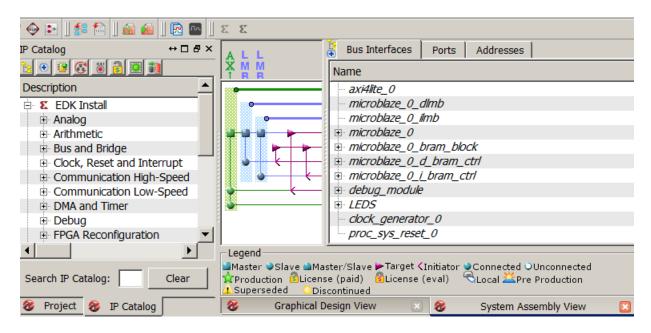

Nach »Finish« öffnet sich im linken Fenster der »IP Catalog« und rechts die »System

Assembly View / Bus Interfaces « (Abb. 6). In diese Ansicht können weitere Komponenten und Busse aus dem Bausteinkatalog zum Rechnersystem hinzugefügt und und verbunden werden. In unserem Projekt hat der »System Builder « bereits alle erforderlichen Bausteile ausgewählt und mit den richtigen Bussen verbunden. Wechsel zum Reiter »Ports.

Abbildung 6: Das konfigurierte System

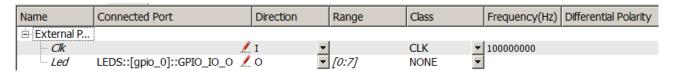

In der Port-Ansicht, Abb. 7, sind die Einträge für die externen Anschlüsse (External Ports) so noch nicht ganz richtig. Unser Rechnersystem benötigt zum Testen keinen Reset-Eingang und der 100MHz-Eingabetakt ist nicht über differentielle Eingänge, sondern nur über einen Eingang an den FPGA angeschlossen. Die Ausgänge zu den Leuchtdioden soll einfach nur »Led« heißen. Der Baustein »clock\_generator« ist in unserem Beispiel, in dem die Frequenz des internen Takts gleich der des Eingangstakts ist, eine einfache Verbindung. Dieser Baustein ist ohne Funktion und soll zur Vereinfachung weggelassen werden.

| Name                       | Connected Port                                        |   | Direction | Range          | Class | Frequency(Hz) |  |

|----------------------------|-------------------------------------------------------|---|-----------|----------------|-------|---------------|--|

| External Ports             |                                                       |   |           |                |       |               |  |

| CLK_N                      | clock_generator_0::CLKIN                              | 1 | I         | ▼              | CLK   | ▼ 100000000   |  |

| CLK_P                      | clock_generator_0::CLKIN                              |   |           | ▼              | CLK   | 100000000     |  |

| - LEDS_TRI_O               | LEDS::[gpio_0]::GPIO_IO_O                             | 1 | 0         | <b>▼</b> [0:7] | NONE  | ▼             |  |

| RESET                      | proc_sys_reset_0::Ext_Reset_In clock_generator_0::RST |   | I         | •              | RST   | _             |  |

| ⊕ axi4lite_0               |                                                       |   |           |                |       |               |  |

| ⊕ microblaze_0_dlmb        |                                                       |   |           |                |       |               |  |

| <i>⊞ microblaze_0_ilmb</i> |                                                       |   |           |                |       |               |  |

| . microblaze_0             |                                                       |   |           |                |       |               |  |

| microblaze_0_bram_block    | k                                                     |   |           |                |       |               |  |

| microblaze_0_d_bram_ct     | rl .                                                  |   |           |                |       |               |  |

| microblaze_0_i_bram_ctri   | 1                                                     |   |           |                |       |               |  |

| ⊕ debug_module             |                                                       |   |           |                |       |               |  |

| ± LEDS                     | ⊕ LEDS                                                |   |           |                |       |               |  |

|                            | ∄ clock_generator_0                                   |   |           |                |       |               |  |

| ⊕ proc_sys_reset_0         |                                                       |   |           |                |       |               |  |

Abbildung 7: Port-Ansicht nach der Konfiguration mit dem »System Builder«

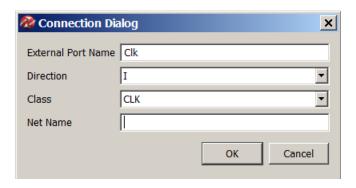

Der einfachste Weg zur Nachbesserung ist, die externen Signale »CLK\_N«, »CLK\_P« und »Reset« sowie den die Taktversorgung »clock\_generator\_0« zu löschen, die Ausgänge

»LEDS\_TRI\_O« in »Led« umzubenenen und die dann fehlenden Verbindungen neu zuzuordnen. Löschen erfolgt durch Mausklick auf den Eintrag und »Delete external Port« bzw. »Delete Instance and all its connections« und erfordert etwas Übung und Geduld. Der neue Taktanschluss wird über einen Klick auf die Schaltfläche ben oben rechts erzeugt. In das aufgehende Menü in Abb. 8 ist der Anschlussnahme, hier »Clk«, die Signalflussrichtung, hier »I« für Eingang/Input, und der Signaltyp, hier »CLK« für Takt einzutragen. Nach »Ok« ist in der Zeile für den Takteintrag noch die Frequenz zu ergänzen (siehe Abb. 9).

Abbildung 8: Dialogfenster für das Anlegen externer Anschlüsse

Namensänderungen erfolgen durch Mausklick auf den alten Namen. Auch das erfordert etwas Übung und Geduld. Abb. 9 zeigt die fertig geänderten Einträge für die externen Anschlüsse.

Abbildung 9: Geänderte Einträge für die externen Anschlüsse

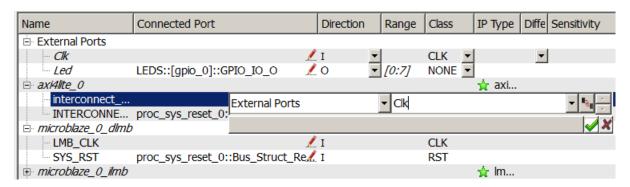

Das Entfernen der Taktversorgung und der externen Anschlüsse hinterlässt offene Eingänge an Bausteinen und entsprechende Fehlermeldungen beim »Design Rule Check« (Run DRCs). An alle offenen Takteingänge (Eingänge der Klasse »CLK«) ist der externe Takt anzuschließen. In Abb. 10 ist für den Takteingang des AXI-Busses das Auswahlmenü für die Zuordnung des Taktanschlusses geöffnet. Am Datenbus »microblaze\_0\_dlmb« darunter ist das Namensfeld für den Taktanschluss noch leer, d.h. der Takteingang ist noch offen².

Abbildung 10: Neuzuordnung des Takts

Insgesamt muss der Takt neunmal angeschlossen werden. Die angeschlossenen Einheiten und ihre Eingabetakte erscheinen auch als »Connected Ports« in der Beschreibungszeile des externen Takteingangs (Abb. 11).

<sup>&</sup>lt;sup>2</sup>Zum Editieren rechte Mouse-Taste auf die Kopfleiste mit Direction, ... und »Net« hinzufügen.

| Name | Connected Port                                                                                                                                                                                                                                                                                                            | Direction | Range | Class |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------|

|      |                                                                                                                                                                                                                                                                                                                           |           |       |       |

| Clk  | proc_sys_reset_0::Slowest_sync_clk microblaze_0_ilmb::LMB_CLK microblaze_0_i_bram_ctrl::[SLMB]::LMB_Clk microblaze_0_dlmb::LMB_CLK microblaze_0_d_bram_ctrl::[SLMB]::LMB_Clk microblaze_0::[DLMB:ILMB:M_AXI_DP:M_AXI_IP]::CLK debug_module::[S_AXI]::S_AXI_ACLK axi4lite_0::[S_AXI]::S_AXI_ACLK LEDS::[S_AXI]::S_AXI_ACLK | I         |       | CLK   |

Abbildung 11: «Connected Ports« am Takteingang

An der Reset-Schaltung müssen außer dem Takt zwei weiteren Eingängen Signalquellen zugeordnet werden. In einem System ohne Reset-Taste ist das Signal »Ext\_Reset\_in« mit dem logischen Wert null (net\_gnd) »Reset inaktiv« und der Eingang »DCM\_lock« mit dem logischen Wert eins (net\_vcc) »Taktversorgung synchronisiert« zu verbinden (Abb. 12). Wenn hier ein Fehler gemacht wird, bleibt der Prozessor dauerhaft rückgesetzt, so dass sich am Ende des Software-Entwurfs kein Programm starten lässt.

| Name                 | Connected Port                                           | Direction   | Range Class |

|----------------------|----------------------------------------------------------|-------------|-------------|

| □ proc_sys_reset_0   |                                                          | ·           |             |

| Slowest_sync_clk     | External Ports::Clk                                      | <u></u> ✓ I | CLK         |

| Ext_Reset_In         | net_gnd                                                  | 🖊 I         | RST         |

| - Aux_Reset_In       |                                                          | <u></u> ✓ I | RST         |

| MB_Debug_Sys_Rst     | debug_module::Debug_SYS_Rst                              | <u></u> ✓ I | RST         |

| Dcm_locked           | net_vcc                                                  | <u></u> ✓ I |             |

| MB_Reset             | microblaze_0::MB_RESET                                   | <u> </u>    | RST         |

| BUS_STRUCT_RESET     | microblaze_0_ilmb::SYS_RST<br>microblaze_0_dlmb::SYS_RST | <i>L</i> o  | RST         |

| ··· Peripheral_Reset |                                                          | <u> </u>    | RST         |

| Interconnect_aresetn | axi4lite_0::INTERCONNECT_ARESETN                         | <u> </u>    | RST         |

| Peripheral_aresetn   |                                                          | <u> </u>    | RST         |

Abbildung 12: Anschlüsse an der Reset-Schaltung

Über dem rechten großen Fenster für die Systembeschreibung gibt es außer »Bus Interfaces« und »Ports« einen dritten Reiter »Adresses«. Über diesen Reiter werden den Speichern und den Registern der peripheren Bausteine Adressbereiche zugeordnet (Abb. 13). Die automatisch generierten Einstellungen sind in Ordnung und verlangen keine Nachbesserung.

| Bus Interfaces   Ports   Addresses |            |              |              |       |                  |              |      |

|------------------------------------|------------|--------------|--------------|-------|------------------|--------------|------|

| Instance                           | Base Name  | Base Address | High Address | Size  | Bus Interface(s) | Bus Name     | Lock |

| ⊟ microblaze_0's Address Map       |            |              |              |       |                  |              |      |

| microblaze_0_d_bram_ctrl           | C_BASEADDR | 0x00000000   | 0x00001FFF   | 8K _  | SLMB             | microblaze_0 |      |

| microblaze_0_i_bram_ctrl           | C_BASEADDR | 0x00000000   | 0x00001FFF   | 8K 🔻  | SLMB             | microblaze_0 |      |

| LEDS                               | C_BASEADDR | 0x40000000   | 0x4000FFFF   | 64K ▼ | S_AXI            | axi4lite_0   |      |

| debug_module                       | C_BASEADDR | 0x41400000   | 0x4140FFFF   | 64K 🔻 | S_AXI            | axi4lite_0   |      |

|                                    |            |              |              |       | _                |              |      |

| <u> </u>                           |            |              |              |       |                  |              |      |

Abbildung 13: Adresszuordnung

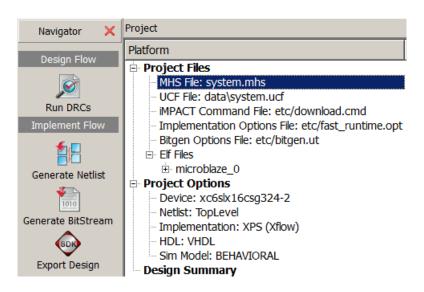

Im nächsten Schritt ist die ucf-Datei zu vervollständigen. Dazu ist unter dem Fenster mit dem IP-Katalog der Reiter »Project« auszuwählen und im Baum »Project Files« die ucf-Datei zu öffnen (Abb. 14). In der automatisch generierten Datei system.ucf steht nur drin, dass der

Takt eine Frequenz von 100 MHz hat. Die Zuordnungen der Gehäuseanschlüsse darunter fehlen und sind selbst einzutragen. Die Pinzuordnungen der in der Abbildung fehlenden Einträge für die Leuchtdioden 3 bis 7 sind in der »nexys3.ucf« auf der Web-Seite zu finden. Wichtig ist, dass die Anschussnamen in der ucf-Datei mit denen der externen Anschlüsse des Rechnersystems übereinstimmen. Zuordnungsfehler bewirken, dass Schaltungsanschlüsse mit falschen Gehäuseanschlüssen verbunden werden. Das wird zum Teil erst beim Programmstart oder der Programmabarbeitung sichtbar.

```

Project

↔□₽×

1

# automatisch generierte Einträge

2

Platform

3

NET "Clk" TNM NET = sys clk pin;

□ Project Files

4

TIMESPEC TS sys clk pin = PERIOD sys clk pin 100000 kHz;

MHS File: system.mhs

UCF File: data\system.ucf

5

iMPACT Command File: etc/do

6

# selbst zu ergänzen

Implementation Options File: 6

NET "Clk"

LOC = "V10" | IOSTANDARD = "LVCMOS33";

LOC = "U16" | IOSTANDARD = "LVCMOS33";

Bitgen Options File: etc/bitgen

NET "Led<0>"

Elf Files

NET "Led<1>"

LOC = "V16" | IOSTANDARD = "LVCMOS33";

9

LOC = "U15" | IOSTANDARD = "LVCMOS33";

10 NET "Led<2>"

```

Abbildung 14: Navigator, Projektdateibaum und ucf-Datei

Die fertige Hardware-Beschreibung steht in der Datei »system.mhs« im Project-File-Baum direkt über der ucf-Datei und kann geöffnet, gelesen und editiert werden (Abb. 15). Von dem gesamten bisherigen Entwurf genügt es, die mhs- und die ucf-Datei aufzubewahren (siehe Anleitungen für die Hardware-Erweiterung des Minimalsystems.

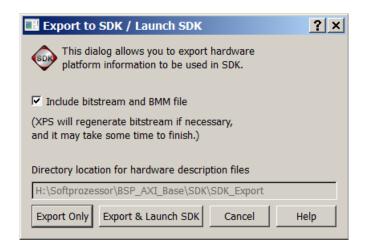

Links neben den »Project Files« befinden sich die Icons der Werkzeuge für die Schaltungserzeugung aus der bis hierher erstellten Konfigurationsbeschreibung. Mit »Run DRLs« wird der »Design Rule Check« gestartet. Dieser kontrolliert die Konfiguration des Rechnersystems auf Zulässigkeit. Er erkennt z.B. offene Takt- und Reset-Eingänge. Sind alle mit »Run DRLs« erkennbaren Fehler beseitigt und wurde für alle möglicherweise noch vorhandenen Warnungen kontrolliert, das sie als ignorierbar gelten³, kann der Generierungsprozess mit »Generate Netlist«, »Generate BitStream« und »Export Design« fortgeführt und abgeschlossen werden.

Abbildung 15: Navigator, Projektdateibaum und ucf-Datei

<sup>&</sup>lt;sup>3</sup>Ignorierte Warnungen bei »Run DRLs« sind oft Ursache für Fehlfunktionen bei der späteren Inbetriebnahme und beim Softwaretest. Es empfielt sich, dazu auffindbare FAQ-Seiten zu studieren. Gefahrenlos ignorierbar sind in der Regel Warnungen, das Lizenzen abgelaufen oder Ausgänge ungenutzt sind.

Die Werkzeuge müssen nicht einzeln aufgerufen werden. »Export Design« mit angekreuztem »Include bitstream and ...« startet alle Bearbeitungsschritte nacheinander (Abb. 16). Mit »Export only« werden die drei Ergebnisdatein des Hardware-Entwurfs für den Software-Entwurf nur gespeichert bzw. überschrieben. »Export & Launch SDK« startet zusätzlich die Software-Entwicklungsumgebung SDK.

Abbildung 16: Auswahlfenster für den Export

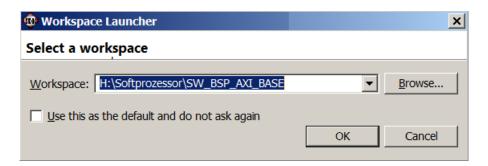

Beim Export und beim Start von SDK ist der Pfad für das Software-Projekt anzugeben (Abb. 17). Das sollte bei einem neuen Projekt ein neu angelegtes leeres Verzeichnis sein.

Abbildung 17: Festlegung des Pfads für das Software-Projekt

SDK hängt sich, wenn es so gestartet wird, gern mit einer Java-Fehlermeldung auf. Dann ist entweder »Export & Launch SDK« noch einmal aufzurufen, aber ohne den Haken bei »Include bitstream and ...« oder SDK ist direkt zu starten. Abb. 18 zeigt das Icon von SDK und den Pfad, unter dem es im Startmenü

### Start ⊳ All Programms

zu finden ist. Beim direkten Start ist der in Abb. 17 festgelegte Workspace auszuwählen.

# 3 Überspringen des Hardware-Entwurfs

Das Ergebnis des Hardware-Entwurfs steht in drei Dateien:

- bit-Datei: Download-File zur Programmierung der Hardware-Funktionalität

- bmm-Datei: Informationen für den Download des Programms und

Abbildung 18: Icon und Pfad für den direkten Start von SDK

• xml-Datei: Informationen, die die Treiber über die Hardware brauchen.

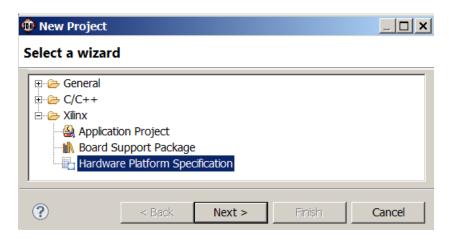

Für den im vorherigen Abschnitt beschrieben Entwurf stehen diese drei Dateien auf der Web-Seite und sind in ein Verzeichnis auf dem Rechner, z.B. »Download« herunterzuladen. Das Entwurfssystem SDK ist normal zu starten und in dem sich öffnenden Fenster genau wie in Abb. 17 ein neues leeres Verzeichnis als »workspace« auszuwählen. Die Auswahl der »Hardware Platform Specification« erfolgt über

### File ▷ New ▷ Project

und dann weiter mit dem Auswahlfenster Abb. 19 und »Next«.

Abbildung 19: Festlegung des Pfads für das Software-Projekt

Im nächsten Fenster, Abb. 20, ist die xml-Datei auszuwählen. Die Auswahl von »Bitstream and BMM Files« darunter, erfolgt, wenn sie im selben Verzeichnis stehen, automatisch. Nach »Finish« wird der Objektbaum für die »Hardware Platform Specification« in derselben Weise wie bei einem Export aus EDK eingerichtet.

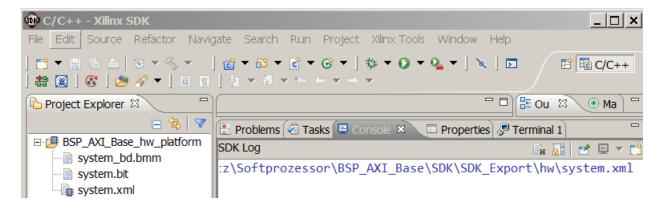

### 4 Software-Entwurf

Nach »Export & Launch SDK« aus EDK bzw. nach »Finish« im Abschnitt zuvor enthält der Objektbaum im »Project Explorer« in Abb. 21 den Teilbaum mit den Dateien zur Beschreibung der Hardware: das bit-File zur Programmierung der Hardware-Funktionalität, das xml-File mit den Hardware-Adressen und Konstanten für die Treiber und das bmm-File, in dem steht, aus welchen Block-RAMs der Befehls- und Datenspeicher zusammengesetzt ist.

Vor dem Entwurf des ersten Anwendungsprogramms ist ein »Board Support Package« mit den hardware-nahen Funktionen und Treibern zu erzeugen. Über

| new Hardware Project                   | _ 🗆 ×  |  |  |  |  |  |

|----------------------------------------|--------|--|--|--|--|--|

| Project name: BSP_AXI_Base_hw_platform |        |  |  |  |  |  |

| ✓ Use default location                 |        |  |  |  |  |  |

| Target Hardware Specification          |        |  |  |  |  |  |

| C:\Users\gkemnitz\Downloads\system.xml | Browse |  |  |  |  |  |

| ► Bitstream and BMM Files              |        |  |  |  |  |  |

| ? < Back Next > Finish                 | Cancel |  |  |  |  |  |

Abbildung 20: Auswahl der Dateien zur Beschreibung der Hardware

Abbildung 21: Projektbaum mit der »Hardware Platform Specification«

File ▷ New ▷ Board Support Pakage

öffnet sich das Fenster in Abb. 22. In ihm ist »standalone« auszuwählen (Entwicklung von Anwendungsprogrammen, die allein ohne Betriebssystem auf dem Prozessor laufen). Im nächsten Fenster ist keine der angebotenen Bibliotheken auszuwählen. Abschluss mit »Ok«.

| New Board Support Package Project      |                                                                                |       |  |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------|-------|--|--|--|--|--|

| Project name: standalone_bsp_0         |                                                                                |       |  |  |  |  |  |

| ✓ Use default location                 |                                                                                |       |  |  |  |  |  |

| Target Hardware                        |                                                                                |       |  |  |  |  |  |

| Hardware Platform:                     | BSP_AXI_Base_hw_platform                                                       | ▼     |  |  |  |  |  |

| CPU:                                   | microblaze_0                                                                   | ⊽     |  |  |  |  |  |

| Board Support Pack                     | rage OS                                                                        |       |  |  |  |  |  |

| xilkernel                              | xilkernel Standalone is a simple, low-level software layer. It provides access |       |  |  |  |  |  |

| standalone to basic processor features |                                                                                |       |  |  |  |  |  |

| ?                                      | Finish Ca                                                                      | incel |  |  |  |  |  |

Abbildung 22: Einrichtung des Board Support Packages

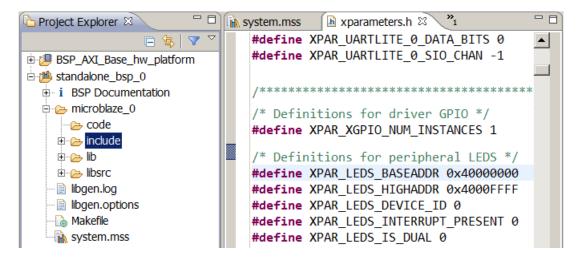

Abb. 23 zeigt den Objektbaum mit dem erzeugten »Board Support Package«. Für die Entwicklung der Anwendungsprogramme sind vor allem die Header im Include-Verzeichnis des Prozessors wichtig. Die hardware-spezifischen Adressen und Konstanten sind hier alle als Makros im Header »xparameters.h« zu finden. »XPAR\_LEDS\_BASEADDR« mit dem Wert 0x40000000000 ist z.B. die Ausgabeadresse an die Leuchtdioden.

Abbildung 23: Projektbaum mit Board Support Package und der Header »xparameters.h«

Nach all den vorbereitenden Schritten kann nun endlich die eigentliche Software-Entwicklung beginnen. Die Einrichtung eines Software-Projekts erfolgt über:

### File $\triangleright$ New $\triangleright$ Application Project

In dem sich öffnenden Fenster, Abb. 24, ist dem Projekt ein Name zu geben, die Programmiersprache festzulegen sowie eine »Hardware Plattform« und ein »Board Support Package« zuzuordnen. Dann geht es mit »Next« zum nächsten Menü.

| new Project                                          |                         |                |        | _ 🗆 🗴  |  |  |  |  |

|------------------------------------------------------|-------------------------|----------------|--------|--------|--|--|--|--|

| Project name: H                                      | Project name: HalloWelt |                |        |        |  |  |  |  |

| Use default location  Target Hardware                |                         |                |        |        |  |  |  |  |

| Hardware Platfor                                     | m BSP_AXI_Ba            | se_hw_platforr | n      | ▼      |  |  |  |  |

| Processor                                            | microblaze_0            | )              |        | ▼      |  |  |  |  |

| Target Software OS Platform Language Board Support P | OS Platform standalone  |                |        |        |  |  |  |  |

| ● Use existing standalone_bsp_0                      |                         |                |        |        |  |  |  |  |

| ?                                                    | < Back                  | Next >         | Finish | Cancel |  |  |  |  |

Abbildung 24: Einrichten eines Software-Projekts

Im nächsten Menü, Abb. 25, wird als Vorlage »Hello World« ausgewählt und das Anlegen des »Applikation Projects« mit »Finish« abgeschlossen. Ergebnis ist der dritter Projektbaum in Abb. 26 mit dem Namen des »Application Projects« und dem »helloworld«-Programm.

Das originale Helloworld-Programm schreibt auf die Standardausgabe den Text »Hello World« und beendet sich. Die Zeile mit der Ausgabe der Konstanten 0xB3 an die Leucht-dioden ist manuell eingefügt. »Xio\_Out8()« ist im Header »xio.h« und die Ausgabeadresse »XPAR\_LEDS\_BASEADDR« in »xparamerters.h« definiert. Das Übersetzen erfolgt beim Speichern. Bei der Fehlermeldung, dass der Übersetzer »XPAR\_LEDS\_BASEADDR« oder

Abbildung 25: Auswahl der Vorlage »Hallo Welt«

»Xio\_Out8()« nicht kennt, fehlt entweder die Inculde-Anweisung für den entsprechenden Header oder der Pfad zum »Board Support Package«. Im letzten Fall empfliehlt es sich, das »Application Project« aus dem Projektbaum zu entfernen, den zugehörigen Verzeichnisbaum zu löschen und das »Application Project« nochmal richtig anzulegen.

```

- -

Project Explorer 🛭

xparameters.h

#include <stdio.h>

#include "platform.h"

■ BSP_AXI_Base_hw_platform

// Header für die LED-Ausgabe

□ 📂 HalloWelt

#include <xparameters.h>

#include <xio.h>

🗓 🍅 Debug

void print(char *str);

Ė ⊕ src

int main(){

⊕ lelloworld.c

init platform();

⊕ latform.c

print("Hello World\n\r");

⊕ h platform.h

XIo_Out8(XPAR_LEDS_BASEADDR, 0xB3);

-- S Iscript.ld

return 0;

```

Abbildung 26: Vollständiger Projektbaum und Anwendungsprogramm

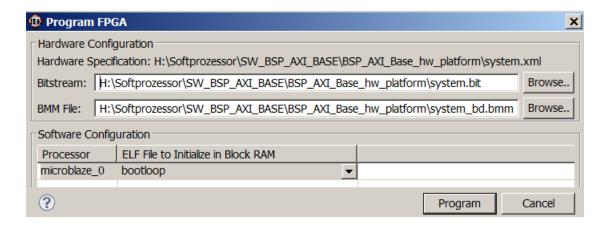

Vor dem Start des Programms ist das Bitfile zur Konfiguration der Rechner-Hardware über das Menü

#### Xilinx Tools ▷ Program FPGA

in den Schaltkreis zu laden. Dabei öffnet sich das Menü in Abb. 27, in dem nur »Program« anzuklicken ist. Falls der Download nicht klappt, ist zu kontrollieren, dass die Baugruppe Strom

Abbildung 27: Programmieren der FPGA-Hardware

Abbildung 28: Grundeinstellungen der »Run Configuration«

hat, angeschaltet und das Programmierkabel angeschlossen ist. Manchmal helfen auch mehrere Versuche, abziehen und wiederanstecken des Programmier-USB-Kabels und vor allem Geduld. Abschließend ist über das Menü

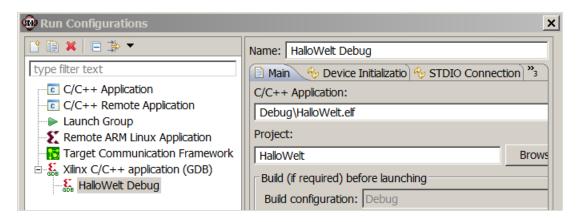

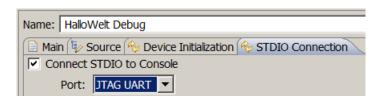

Run  $\triangleright$  Run Configurations.. $\triangleright$  »Xilinx c/C++ application (GDB)

mit einem Rechtsklick auf »Xilinx c/C++ applicatiion (GDB)« eine »Launch Configuration« zu erzeugen. Unter dem Reiter »Main« bekommt diese einen Namen, ein Projekt, ein ausführbares Programm, ... zugeordnet (Abb. 28). In unserem Projekt ist nur unter dem Reiter »STDIO Connection« eine Änderung erforderlich (Abb 29). Hier ist »Connect STDIO to Console« und als Port »JTAG UART« auszuwählen.

Abbildung 29: Verbindung der Standardausgabe mit der Konsole

Der Programmstart erfolgt mit »Run« bzw. über die Schaltfläche ☑. Nach Laden und Programmstart gibt unser Beispielprogramm auf der Konsole den Text »Hello World« aus (Abb. 30). Das Ausgabebitmuster auf den Leuchtdioden ist »1100 1101« (der bitgespiegelte Wert zu 0xB3).

Abbildung 30: Testausgabe auf der Console