## Integration eigener Hardware-Bausteine

Prof. G. Kemnitz, TU Clausthal, Institut für Informatik 22. April 2016

## Zusammenfassung

Das in der vorherigen Anleitung erzeugte System wird in dieser Anleitung um integrierten Logikanalysator für unterschiedliche Testaufgaben erweitert. Zuerst sollen in analoger Weise wie in Anleitung 3 die Trace- und Led-Signale für einen inneren Schleifendurchlauf beim Hochzählen eines Led-Ausgabewerts untersucht werden. Ziel ist die Abschätzung, wie lange der Schreibzugriff über den LMB auf ein Ausgaberegister dauert. Im zweiten Versuch werden die Ausgabesignale des Festwert-Timers FIT1, und wie lange die Programmreaktion auf ein Timer-Event dauert, untersucht. Im dritten Versuch werden die Signale auf dem LMB untersucht. Da es für den LMB keinen Busanalysator wie für den AXI-Bus gibt, wird ein anderes Werkzeug, der »ChipScope Core Inserter« genutzt. Mit dem »Core Inserter« lassen sich auch alternative Signale als Aufzeichnungstakt verwenden. Als Beispiel hierfür wird im letzten Versuch ein integrierter Logikanalysator für die Aufzeichnung des UART-Sende- und Empfangssignal mit dem 500 kHz Signal am Toggle-Ausgang von FIT1 getaktet.

## 1 Kopieren des LMB-IO-Systems in ein neues Projekt

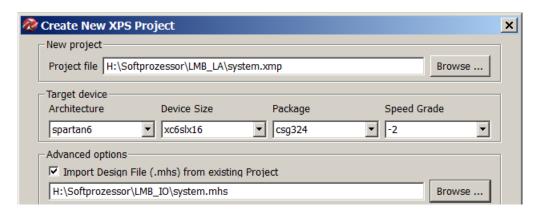

Um das Projekt der vorherigen Anleitung nicht zu verändern, werden die Entwurfsergebnisse in Form der mhs- und der ucf-Datei in ein neues Projekt übernommen. Dazu ist in EDK ein neues Projekt zu erzeugen. In dem sich öffnenden Fenster ist der FPGA-Typ und das mhs-File des vorherigen Projekts wie in Abb. 1 auszuwählen<sup>1</sup>. Nach Erzeugen des neuen Projekt ist die Datei »system.ucf« im Unterverzeichnis »/data« durch die des vorherigen Projekts zu ersetzen.

Abbildung 1: Erzeugung eines neuen Projekts der bisherigen Schaltung

Abb. 2 zeigt das Blockschaltbild des importierten Rechnersystems ohne integrierte Logikanalysatoren. Es enthält den Prozessor mit je einem LMB (local memory busses) für Befehle

<sup>&</sup>lt;sup>1</sup>Alle Auswahlfelder darunter sind abzuwählen.

und Daten. Beide LMB's sind über einen Speicher-Controller mit je einem Port des Dual-Port-Block-RAM's verbunden. Zusätzlich ist am Daten-LMB das IO-Modul mit den parallelen Schnittstellen, Timern und der UART angeschlossen. Nur der Debug-Controller nutzt weiterhin den AXI-Bus.

Abbildung 2: Rechnersystem ohne integrierte Logikanalysatoren

In Vorbereitung des Tests mit einem integrierten Logikanalysator empfiehlt es sich, den zu beobachtenden internen Signalen und den Bausteinen, deren Anschlussignale zu beobachten sind, eigene aussagekräftige Namen zu geben. Das geht am einfachsten mit »Replace All« im mhs-File. Die internen Anschlusssignale sollen den Port-Namen mit angehängtem »\_x«, der Prozessor den Namen »cpu«, die lokalen Speicherbusse die Namen »ilmb« und »dlmb« (i –

```

PORT Clk = Clk_x, DIR = I,...

. . .

PORT sw = sw_x, DIR = I,..

END

PORT btn = btn_x, DIR = I,..

BEGIN lmb_bram_if_cntlr

PORT Led = led_x, DIR = 0,...

PARAMETER INSTANCE = dbram_cntlr

PORT seg = seg_x, DIR = 0,...

PORT an = an_x, DIR = 0,...

END

PORT RsRx = Rx, DIR = I

BEGIN lmb_bram_if_cntlr

PORT RsTx = Tx, DIR = 0

PARAMETER INSTANCE = ibram_cntlr

PORT T500kHz = T500kHz_x, DIR = 0

BEGIN microblaze

END

PARAMETER INSTANCE = cpu

BEGIN bram_block

. . .

PARAMETER INSTANCE = bram

END

BEGIN lmb_v10

END

PARAMETER INSTANCE = ilmb

BEGIN iomodule

. . .

PARAMETER INSTANCE = io

END

BEGIN lmb_v10

PORT FIT1_Toggle = T500kHz_x

PARAMETER INSTANCE = dlmb

END

```

Abbildung 3: Umbenennungen und Ergänzungen im mhs-File

instruction; d – data), die Speicher-Controller die Namen »ibram\_cntrl« und »dbram\_cntrl« und der Block-Ram den Namen »bram« bekommen (Abb. 3). Für den letzten Versuch mit dem 500 kHz-Toggle-Ausgang von Timer »FIT1« als Aufzeichnungstakt des Logikanalysators ist es erforderlich, den Toggle-Ausgang des Timers als Schaltungsausgang herauszuführen².

<sup>&</sup>lt;sup>2</sup>Der Netzlistengenerator des IO-Moduls erzeugt sonst keinen Toggle-Ausgang für FIT1.