Lehre.Praktikum_VHDL1 (Struktur)

Praktikum digitaler Schaltungsentwurf I

|

(G. Kemnitz, C. Giesemann)

Betreute Laborübungen zur Einführung in den rechnergestützten Entwurf, die Simulation, die Synthese und den Test digitaler Schaltungen. Die Schaltungen werden in VHDL beschrieben, simuliert, synthetisiert etc. und abschließend zum Testen in programmierbare Logikschaltkreise geladen. ... |

|

Der Test und die Fehlersuche erfolgt mit Hilfe der Ein- und Ausgabeelemente auf der Versuchsbaugruppe, einem integrierten Logikanalysator und einem USB-Logikanalysator. Die Laborübung wird von einem Mitarbeiter oder einem Hilfswissenschaftler betreut. Für jede Aufgabe sind eine bis zwei 90-minütige Übungen eingeplant.

Zielgruppe: Bachelor Technische Informatik; Interessenten Credits: (ECTS): 3 |

Aufgaben

| Aufgabenstellung | Thema | Abgabeblatt | Datenblätter und Programmbausteine |

|---|---|---|---|

| [VH1] | Entwurf, Simulation und Test einer kombinatorischen Schaltung | [A1] | [PrakVHDL1_1.zip] |

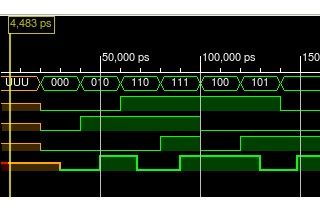

| [VH2] | Linear rückgekoppelte Schieberegister, ChipScope und Logikanalysator | [A2] | [PrakVHDL1_2.zip] |

| [VH3] | Asynchrone Eingabe | [A3] | |

| [VH4] | 7-Segment-Anzeige | [A4] | |

| [VH5] | Zahlenschloss | [A5] | |

| [VH6] | Ampelsteuerung | [A6] | |

| [VH7] | Serielle Schnittstelle | [A7] | [PrakVHDL1_7.zip] |

Weitere Informationen und Dokumentationen

- Schritt-für-Schritt-Anleitung für den Schaltungsentwurf mit ISE

- [Dokumentation zum USB-Logikanalysator]

- Beschreibung des Versuchs-Boards

Autor: gkemnitz, Letzte Änderung: 26.03.2026 16:34:28

TU Clausthal 2020 Impressum