## Grundlagen der Digitaltechnik Große Übung 6

Prof. G. Kemnitz, Dr. C. Giesemann

Institut für Informatik, Technische Universität Clausthal 14. April 2021

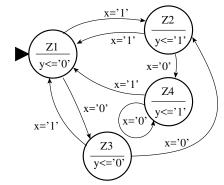

#### Aufgabe 6.1: Zustandsgraph $\Rightarrow$ Übergangstabelle

- Zustandswechsel bei steigender Taktflanke

- Initialisierung mit highaktivem Initialisierungssignal

| symbolische Zustandsbezeichnung | Z1   | Z2   | Z3   | Z4   |

|---------------------------------|------|------|------|------|

| Zustandsvektor                  | "00" | "01" | "10" | "11" |

Ausfüllen der Übergangstabelle

| Eingabe      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

|--------------|----|----|----|----|----|----|----|----|

| Zustand      | 00 | 00 | 01 | 01 | 10 | 10 | 11 | 11 |

| Ausgabe      |    |    |    |    |    |    |    |    |

| Folgezustand |    |    |    |    |    |    |    |    |

- Skizze der Gesamtschaltung (Eingabeabtastung, Zustandsregister, Übergangs- und Ausgabefunktion als Black-Box).

- 3 Wie viele Speicherzellen benötigt der Automat?

- 4 Beschreibung in VHDL (Entity- und Architecture-Teil).

# Aufgabe 6.2: Verbale Beschreibung $\Rightarrow$ Zustandsgraph

Entwerfen Sie den Zustandsgraphen für einen Automaten mit den zwei bitorientierten Eingabesignalen a und b, dem high-aktiven Initialisierungssignal I und den Zuständen Z0 bis Z5, der

- lacksquare zu Beginn und bei I=1 in den Zustand Z0 übergeht,

- lacksquare sonst von jedem Zustand bei a=1 in den Zustand Z5 übergeht,

- lacksquare sonst bei b=1 die Zustandsfolge zyklisch durchläuft und

- sonst in seinem Zustand verbleibt.

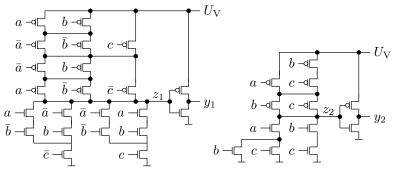

#### Aufgabe 6.3: Entwurf FCMOS 1

Entwerfen Sie ein FCMOS-Gatter mit der nachfolgenden Funktion:

$$y = \overline{a \vee b} \vee \bar{c}$$

#### Aufgabe 6.4: Entwurf FCMOS 2

Vereinfachen Sie die nachfolgenden Ausdrücke so weit wie möglich:

- $1 x_1x_2x_4 \vee x_1x_4 \vee \bar{x}_1x_2x_4$

- $(x_1 \lor x_2 \lor \bar{x}_3) (\bar{x}_1 \lor x_3)$

Bilden Sie die vereinfachten logischen Ausdrücke durch FCMOS-Gatter nach.

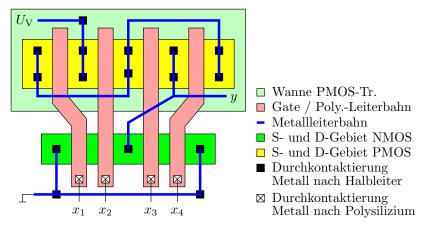

### Aufgabe 6.5: Logische Funktion gesucht

- Zerlegung in einzelne Gatter.

- Bestimmung der Funktionen der NMOS- und der PMOS-Netzwerke.

- Bestimmung der Gatterfunktionen und der Gesamtfunktionen.

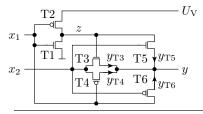

#### Aufgabe 6.6: Schaltung mit Transfergattern

| $x_2$ | $x_1$ | z | $y_{\mathrm{T3}}$ | $y_{\mathrm{T4}}$ | $y_{T5}$ | $y_{\rm T6}$ | y |

|-------|-------|---|-------------------|-------------------|----------|--------------|---|

| 0     | 0     |   |                   |                   |          |              |   |

| 0     | 1     |   |                   |                   |          |              |   |

| 1     | 0     |   |                   |                   |          |              |   |

| 1     | 1     |   |                   |                   |          |              |   |

$$\begin{array}{ccc}

1 & & & & & \\

1 & \longrightarrow H & & & & & \\

\end{array}$$

zu unterstellendes Verhalten für einen NMOS-Transistor, der eine Eins und einen PMOS-Transistor der eine Null weiterleitet

- **II** Füllen Sie die Tabelle mit den logischen Werte von z und den von T3 bis T5 weitergeleiteten Werten aus<sup>1</sup>.

- $lue{y}$  Bestimmen Sie die Werte von y und die logische Funktion.

<sup>1</sup>Ein ausgeschalteter Transistor gibt <sup>'</sup>Z', ein eingeschalteter NMOS-Transistor gibt <sup>'</sup>0' oder 'H' und ein eingeschalteter PMOS-Transistor '1' oder 'L' weiter.

### Aufgabe 6.7: Rückgewinnung Transistorschaltung

- **I** Lesen Sie die Transistorschaltung ab.

- 2 Bestimmen Sie die logische Funktion des Gatters.

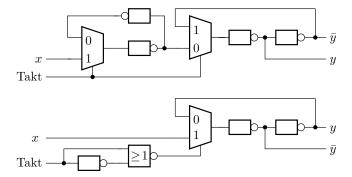

#### Aufgabe 6.8: Speicherzellen entwickeln

Entwickeln Sie die Schaltung für zwei 1-Bit-Registerzellen aus logischen Gattern und Multiplexern:

- Die erste soll nach dem Master-Slave-Prinzip arbeiten und die Eingabedaten mit der fallenden Taktflanke an ihren Ausgang übernehmen.

- 2 Die zweite soll eine gepulste zustandsgesteuerte Zelle sein, die den Übernahmeimpuls aus der fallenden Taktflanke ableitet.

#### Zur Kontrolle