# Grundlagen der Digitaltechnik Große Übung 4

Prof. G. Kemnitz, Dr. C. Giesemann

Institut für Informatik, Technische Universität Clausthal 14. April 2021

# Aufgabe 4.1: Extraktion des Signalflussplans

```

signal x, tmp, acc, y: std_logic_vector(3 downto 0);

signal op: std_logic_vector(1 downto 0);

signal T: std_logic;

process(T)

begin

if rising_edge(T) then

case op is

when "00" => acc <= x;

when "01" => acc <= acc + tmp;

when "10" => acc <= acc - tmp;

when others => null;

end case;

tmp <= x;

Bilden Sie den Berechnungfluss

end if;

durch eine Schaltung aus Registern,

end process;

Rechenwerken und Multiplexern nach.

y <= acc;

```

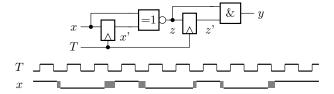

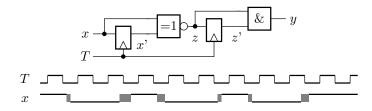

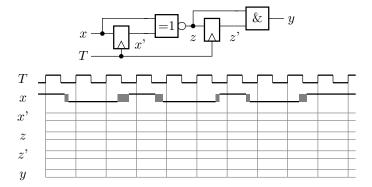

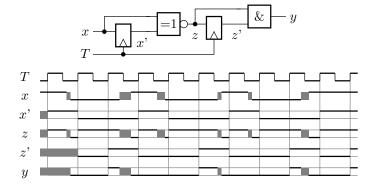

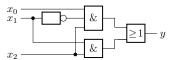

## Aufgabe 4.2: Logikfunktion mit Zwischenabtastung

Bestimmen Sie für die gegebene Schaltung und den gegebenen Eingabesignalverlauf die Signalverläufe der Zwischensignale x', z, z' und des Ausgabesignals y.

(Vorhalte-, Halte- und Verzögerungszeiten der Gatter und Speicherzellen seien gegenüber der Taktperiode vernachlässigbar.)

# TU Clausthal

#### Hinweise:

- Der Zeitverlauf der unabgetasten Eingabe wirkt ohne zeitliche Ausrichtung bis auf das Ausgabesignal.

- Wenn ein Eingang der UND-Verknüpfung 0 und der andere ungültig ist, ist die Ausgabe 0.

## Lösung

#### Zur Kontrolle

## Aufgabe 4.3: Asynchrone parallele Übertragung

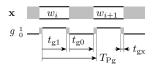

Bei einer asynchronen Übertragung seien die mit dem Signal  ${\bf x}$  übertragenen Datenworte immer dann gültig, wenn das mit übertragene Gültigkeitssignal  $g \neq 0$  ist:

$$\begin{array}{ll} t_{\rm g0} & {\rm Mindest dauer} \ g = 0 \\ t_{\rm g1} & {\rm Mindest dauer} \ g = 1 \\ t_{\rm gx} & {\rm Maximal dauer} \ g = {\rm X} \end{array}$$

$$T_{\text{Pg}}$$

Periodendauer von  $g$

- Mit welcher Taktfrequenz muss die Empfangsschaltung die beiden Signale mindestens abtasten<sup>1</sup>?

- Wie ist das Gültigkeitssignal für die abgetasteten Datenworte zu bilden, damit es für jedes abgetastete gültige Datenwort genau einen Takt lang aktiv ist?

<sup>&</sup>lt;sup>1</sup>Zeit für q = 0 gleich Zeit für q = 1

## Aufgabe 4.4: Schaltungsumformung

Suchen Sie nach Vereinfachungsmöglichkeiten:

$$x_1x_2\left(x_2\vee x_3\right)\vee x_4\left(x_1x_2\vee x_2\right)$$

Wandeln Sie die nachfolgende Schaltung in eine Schaltung aus NAND-Gattern und Invertern um.

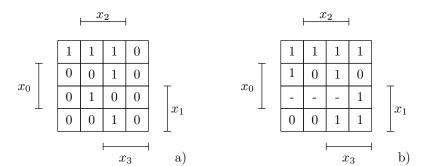

### Aufgabe 4.5: Vereinfachung mit KV-Diagrammen

# Aufgabe 4.6: Schaltungsminimierung nach Quine und McCluskey

Gegeben ist die Menge Minterme, für die der Funktionswert »1« ist:

$$K \in \{100000, 100100, 101010, 101110, 111110, 110000, 011000, 101011, 101111, 101000, 101001\}$$

- Erstellen Sie die quineschen Tabellen.

- 2 Stellen Sie die Tabelle der Primterme auf.

- 3 Suchen Sie eine minimale Abdeckungsmenge.

# Aufgabe 4.7: VHDL, Wertetabelle, ROBDD, Schaltung

```

signal a, b, c, y: std_logic;

...

y <= a xor b xor c;</pre>

```

- Stellen Sie die Wertetabelle für die Schaltung auf.

- Entwickeln Sie aus der Wertetabelle das unreduzierte OBDD für die Abfragereihenfolge a-b-c.

- Entwickeln Sie mit Hilfe der Vereinfachungsregeln Verschmelzung und Knotenelimination – das zugehörige ROBDD.

- Intwickeln Sie aus dem ROBDD eine optimierte Schaltung.