Einführung in ISE

Start des Entwicklungssystems unter Linux

Über das Menü Anwendungen => Umgebung => Xilinx ISE 9.2

Anlegen eines neuen Projektes

Auswahl Menuepunkt "File"

Auswahl Menuepunkt "New Projekt"

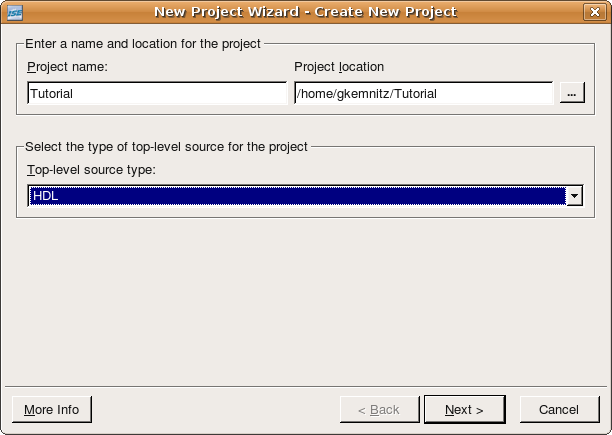

Projektnamen und Verzeichnis wählen

Bitte beachten: Der Pfad muss in ihr eigenes Homeverzeichnis zeigen. Sonst fehlen Ihnen die Schreibrechte.

In diesem Beispiel wurde als Name "Tutorial" und als Ort das eigene Home-Verzeichnis gewählt. Das "Tutorial" am Ende vom Pfad wurde automatisch hinzugefügt. Es dürfen keine Leerzeichen im Projektpfad stehen.

Als Modultyp wird die Voreinstellung "HDL" belassen.

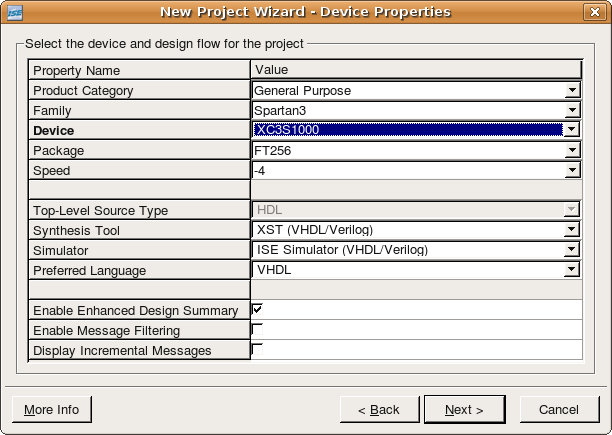

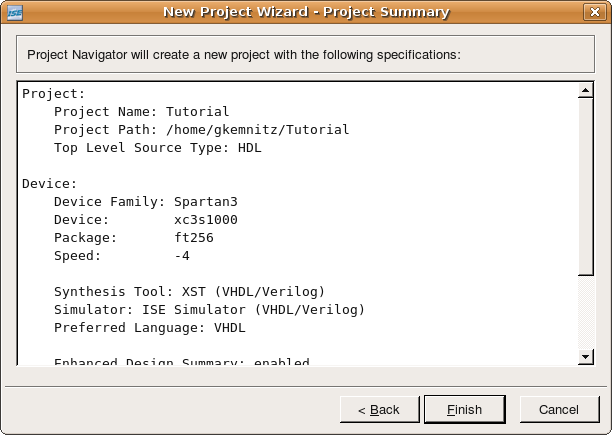

Zielhardware angeben

- Produktkategorie: allgemeine Verwendung

- Schaltkreisfamilie: Spartan3

- Schaltkreisbezeichnung: xc3s1000

- Gehäusetyp: ft256

- Geschwindigkeitsklasse: -4

- Synthesewerkzeug: XST

- Simulator: ISE Simulator

- Bevorzugte Sprache: VHDL

Typ, Gehäuse und Geschwindigkeitsklasse stehen auf dem Schaltkreis.

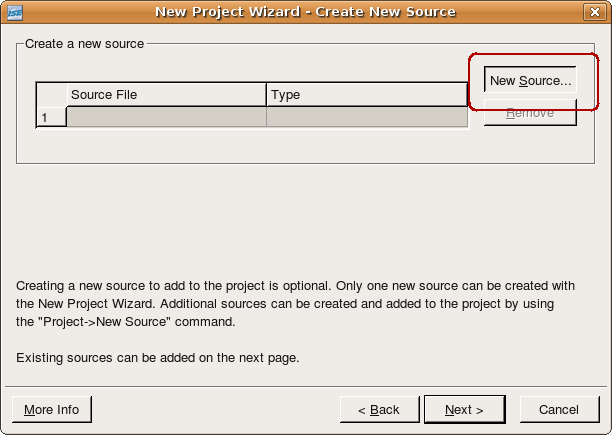

VHDL-Datei erstellen

Die in den Schaltkreis zu programmierende Funktion wird in einer oder mehreren VHDL-Dateien beschrieben. In unserem 1. Beispiel soll nur eine VHDL-Datei erzeugt werden. Zum Anlegen dieser VHDL-Datei "New Source" auswählen.

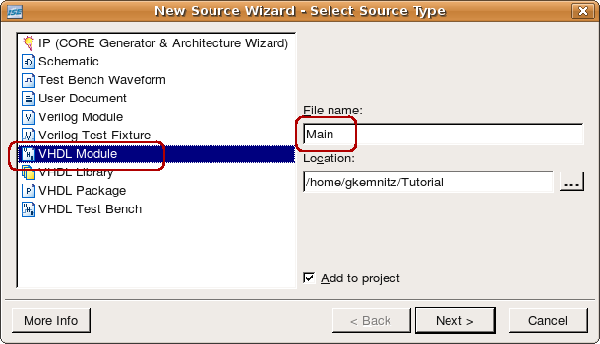

Für die neu anzulegende Datei müssen Name und Typ festgelegt werden. Typ ist VHDL-Module.

Name sei "Main".

Klicken sie auf "Next"

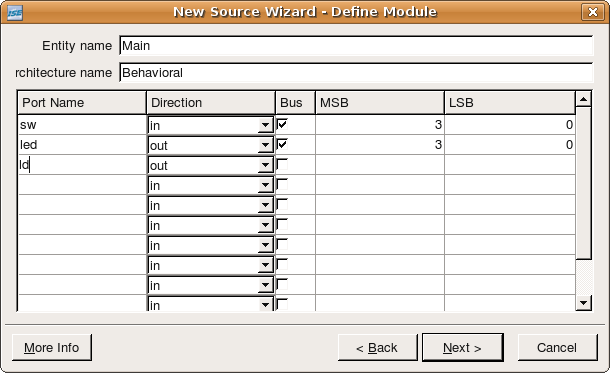

Anschlüsse (Ports) der Schaltung festlegen

Das nachfolgende Menu bietet eine Möglichkeit, Bezeichnung, Signalflussrichtung und Typ der Schaltungsanschlüsse festzulegen. Alternativ kann das Menue mit "Next" übersprungen und der Entity-Teil der Schaltungsbeschreibung später mit dem Text-Editor eingegeben werden.

Wir wollen im Beispiel folgende Anschlüsse definieren:

- SW: in std_logic_vector(0 to 3); -- Eingabe: 4 Schalter

- LD: out std_logic_vector(0 to 3); -- Ausgabe: 4 Leuchtdioden

- LD7: out std_logic; -- Ausgabe: Einzelleuchtdiode

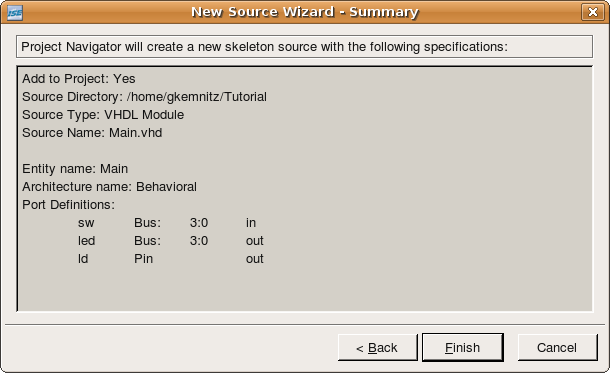

Abschließend alle Einstellungen kontrollieren und mit "Finish" bestätigen.

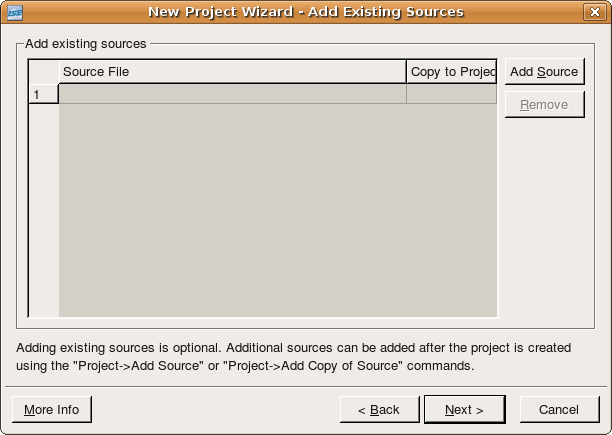

Wenn keine weiteren neuen Dateien erstellt werden sollen, weiter mit "Next" zum "Add Source"-Dialog.

In den kommenden Übungen werden Sie mit diesem Menue vorhandene VHDL- und ucf-Dateien in das aktuelle Projekt einbinden. Diese Dateien müssen Sie aus dem Netz in das Projektverzeichnis kopieren und dann mit "Add Source" einbinden. Jetzt "Next".

Abschließend alle Eingaben überprüfen und den Projekt-Assistenten schließen.

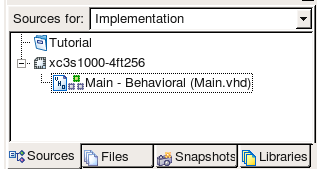

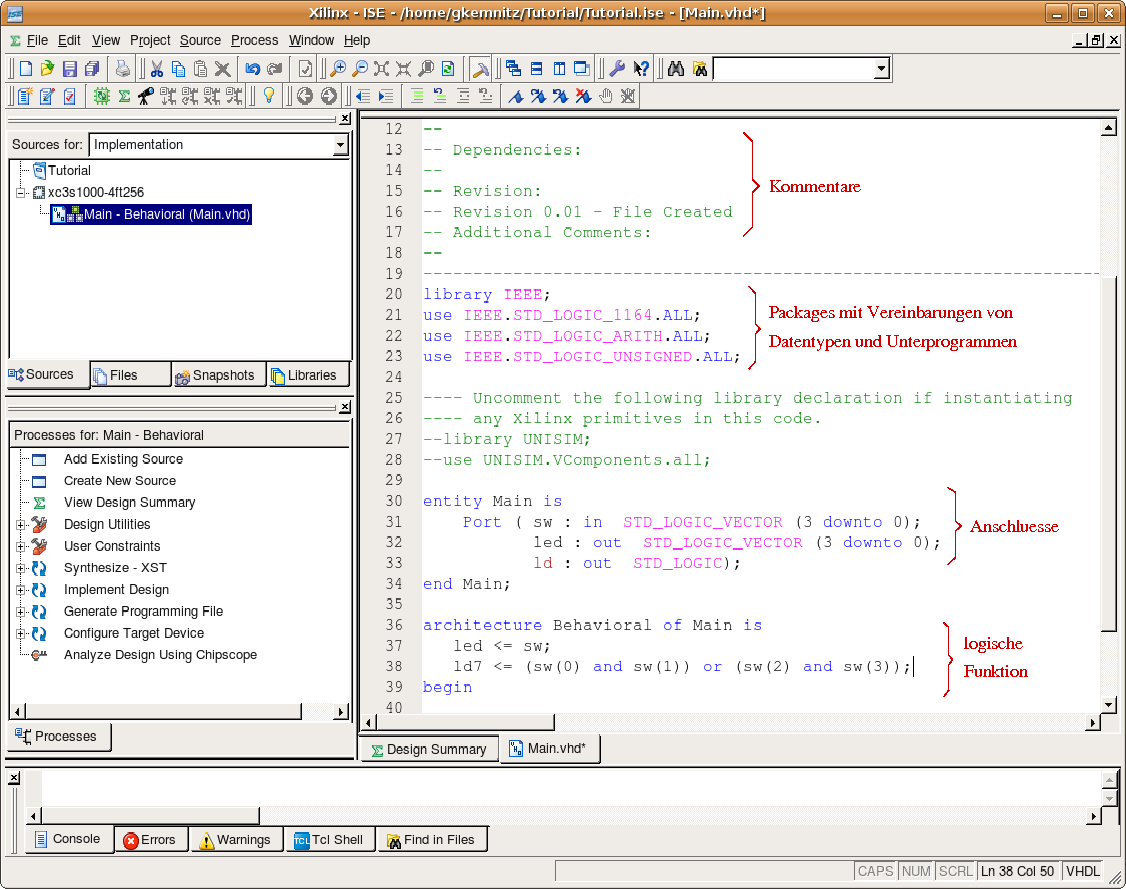

Beschreibung der Oberfläche

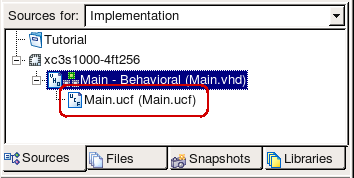

Im Source-Fenster (oben links im Projektfenster) werden alle im Projekt eingebundenen Quell-Dateien in Form eines Abhängigkeitsbaums angezeigt.

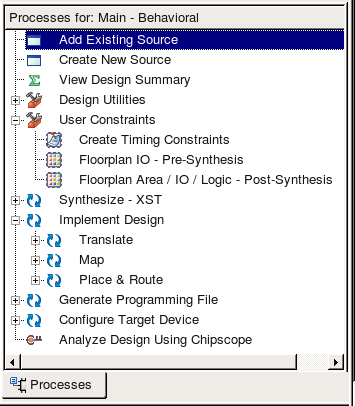

Process-Fenster

In Abhängigkeit vom Typ der ausgewählten Datei erscheinen im Fenster darunter alle Werkzeuge, die auf die ausgewählte Datei angewendet werden können. Darüber hinaus können auch hier mit "Create New Source" neue Projektdateien erzeugt und mit "Add Existing Source" existierende (im Projektverzeichnis gespeicherte) Dateien eingebunden werden.

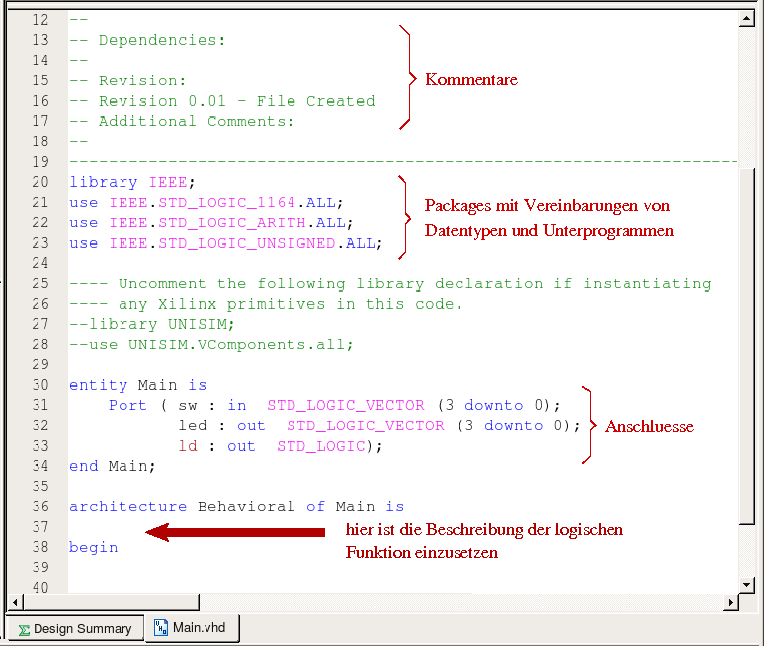

In dem großen rechten Fenster wird der Inhalt eines ausgewählten Entwurfsobjekts, in der Abbildung der Inhalt der Datei Main.vhd, angezeigt. VHDL-Dateien können hier editiert werden.

Ganz unten ist der Statusbereich des Programms. Bei Fehlern lohnt es sich, etwas zurückzuscrollen und die Fehlermeldung zu studieren. Bei den meisten Fehlermeldungen gibt es die Möglichkeit, das "WEB"-Symbol mit der rechten Maustaste anzuclicken und sich dann die Hilfeseite bei Xilinx anzusehen (Xilinx ist der Hersteller hier eingesetzten programmierbaren Logikschaltkreise).

Bearbeitung der Schaltungsbeschreibung

Falls noch nicht erfolgt, öffnen der Datei Main.vhd mit Doppelklick. Ergänzen der logischen Beschreibung.

Im Beispiel werden die Logikwerte der Eingabesignale von den Schaltern an die Leuchtdioden LD0 bis LD3 ausgegeben. An LD7 wird eine logische Verknüpfung ausgegeben.

Speichern (Diskettensymbol, Str-S etc.).

Zuordnung von Gehäuseanschlüssen zu Signalnamen der VHDL-Datei

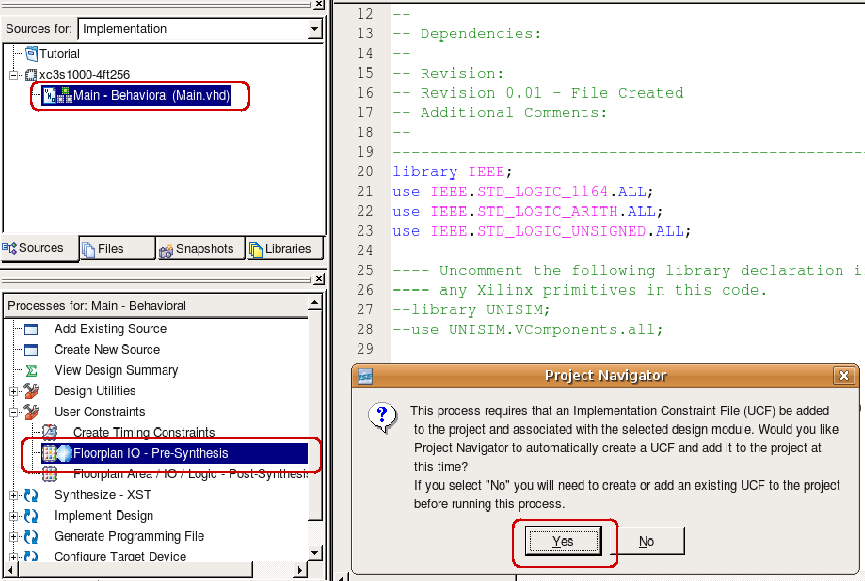

Auswahl von Main.vhd im linken oberen Fenster.

Aufklappen des Teilbaums "User Constraints" im Process-Fenster

Auswahl "Floorplan IO - Pre-Synthesis". Wenn das Projekt wie in unserem Fall noch keine .ucf-Datei hat, stellt das System die Frage, ob eine ucf-Datei angelegt werden darf. "Yes".

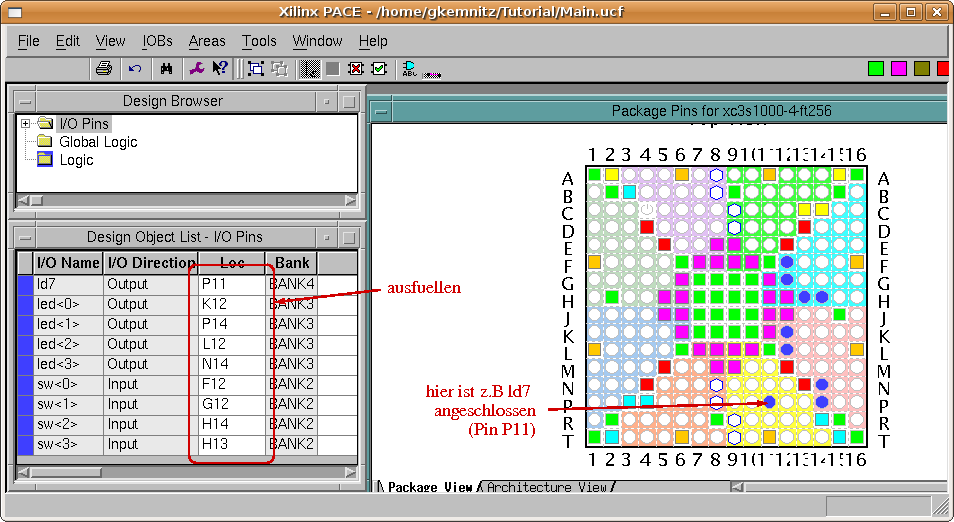

Im Constraints-Editor (PACE) ist jetzt nur der untere linke Bereich interessant. Dort erscheinen die Schaltungsanschlüsse, denen Schaltkreisanschlüsse zugeordnet werden müssen.

Um einem Signal einen Pin zuzuweisen, clickt man in das Loc-Feld des Signals. Nicht die Drop-Down-Liste Verwenden! Pin-Nummer des Signals eintragen. Diese Nummern stehen im Schaltplan und in der technischen Dokumentation der Baugruppe. Die einzutragenden Werte stehen im Bild. Das rechte Bild die Zuordnung zu den Gehäuseanschlüssen.

Für spätere Entwürfe mit größerer Anschlusszahl bekommen Sie eine fertige ucf-Datei mit den Pin-Zuordnungen für alle Schaltkreisanschlüsse, die in das Projektverzeichnis zu kopiere und mit "Add Existing Source" einzubinden ist.

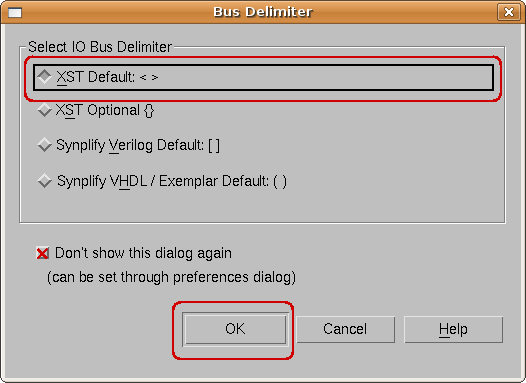

Speichern mit File->Save. Im folgenden Fenster die Option "XST Default: <>" wählen und mit "OK" bestätigen. Das Programm "Pace" schließen.

Im Source-Bereich (oben links) erscheint die UCF-Datei, die jetzt beispielsweise auch mit "Edit Constraints (Text)" als Textdatei bearbeitet werden kann.

Projekt übersetzen

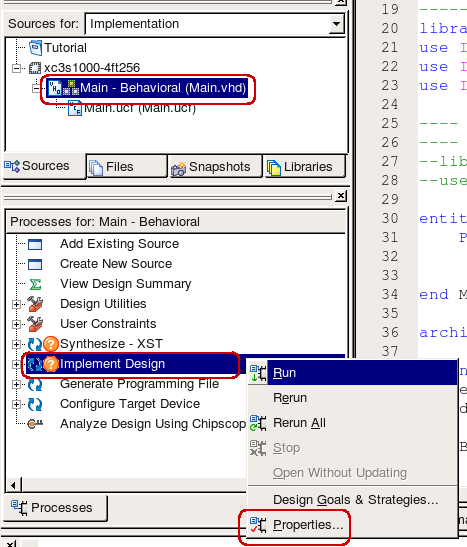

Einstellungen für den Übersetzungsprozess

Für alle nachfolgenden Projekte verwenden Sie eine ucf-Datei, die die Pinzuordnung für alle am Schaltkreis angeschlossenen Taster, Leuchtdioden etc., d.h. auch für Anschlüsse, die in den Aufgaben nicht genutzt werden, enthält. Das System akzeptiert normalerweise solche ungenutzten, aber in der ucf-Datei aufgeführten Anschlüsse nicht. Damit die zugehörigen loc-Einträge nicht auskommentiert werden müssen, empfiehlt es sich, in "Implement Design Properties" das Flag "Allow Unmached LOC Constraints" zu setzen.

Unten links mit der rechten Maustaste auf "Implement Design" clicken. und "Properties" auswählen.

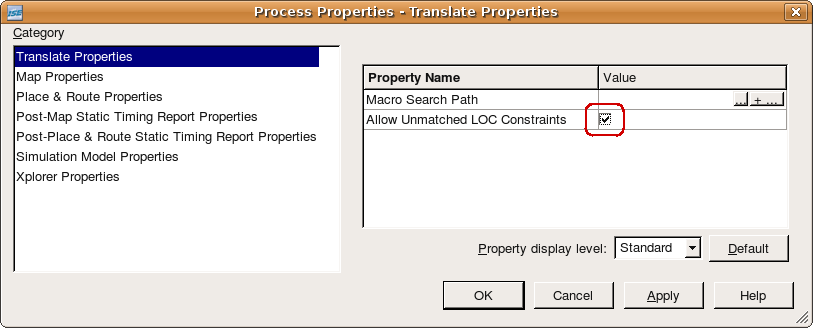

"Translate Properties" auswählen und "Allow Unmatched LOC Constraints" aktivieren.

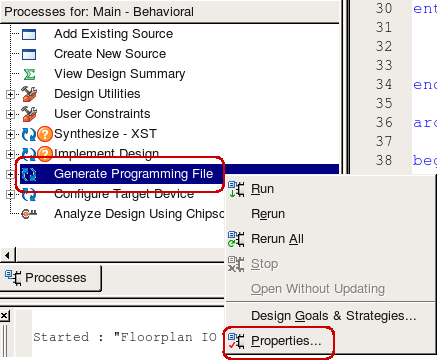

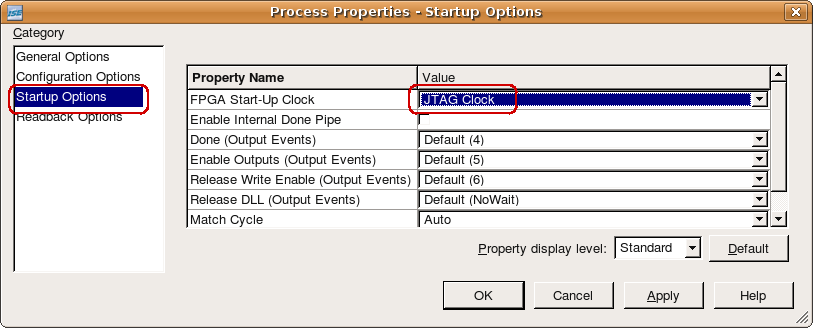

In der Übung benutzen wir statt der Standard-Download-Methode "Programmieren über JTAG". JTAG ist ein Test- und Programmierbus. Die Umstellung auf JTAG erfordert, dass das Attribut "FPGA Start-Up Clk" in "JTAG Clock" geändert wird.

Unter "Generate Programming File" mit der rechten Mousetaste "Properties" öffnen, "Startup Options" aktivieren und darin "FPGA Start-Up Clock" in "JTAG Clock" umändern.

Konfigurationsdatei für den programmierbaren Logikschaltkreis erzeugen

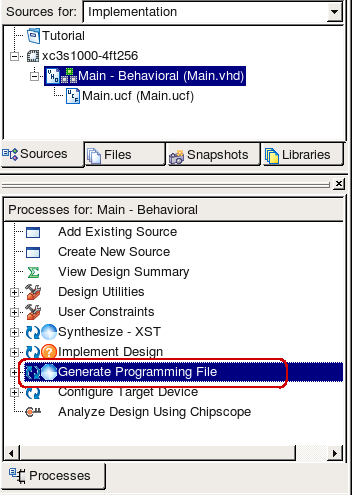

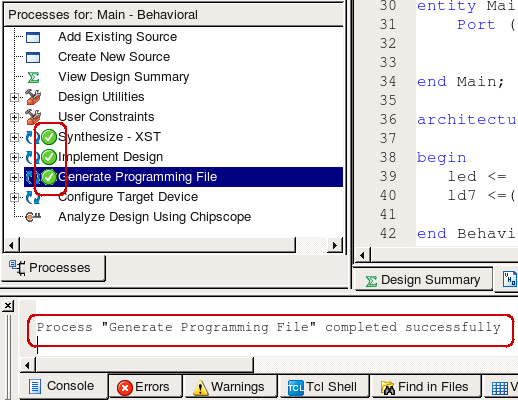

Main.vhd im Source-Fenster auswählen und im Process-Fester Doppelclick auf "Generate Programming File".

Die Berechnung der Konfigurationsdatei besteht aus den Schritten: Synthese (Berechnung der Schaltung aus der VHDL-Beschreibung), "Implement Design" (Anordnung und Verdrahtung der einzelnen Schaltungsbausteine (Gatter etc.)) und "Generate Programming File" (Berechnung der Konfigurationsdaten aus den geometrischen Daten) und dauert einige Zeit. Erfolgreich berechnete Zwischenergebnisse werden durch Meldungen im Statusfeld und grüne Haken im Process-Fenster signalisiert. Bei einem erkannten Fehler in einer Source-Datei bricht der Prozess ab. Der Fehler muss manuell beseitigt und der Prozess neu gestartet werden.

Download

Netzteil der Baugruppe in die Steckdose stecken, evt. Schalter "FPGA" betätigen.

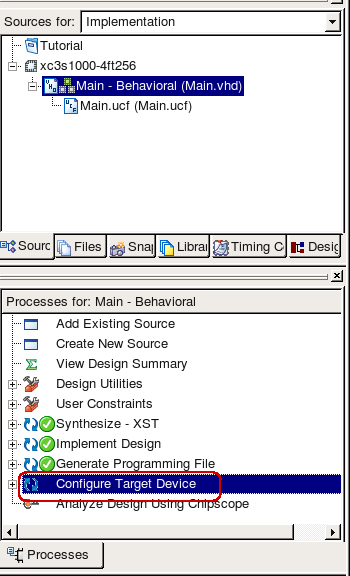

Unter "Generate Programming File" auf "Configure Device (iMPACT)" Doppelklick.

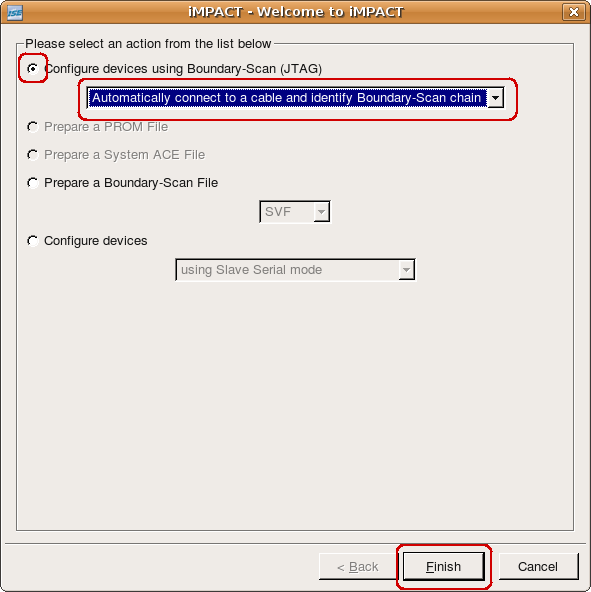

"Boundary Scan Mode" auswählen. ("Boundary Scan" bedeutet hier dasselbe wie JTAG. Boundary-Scan ist die Bezeichnung für den Testbus, der hier zum Programmieren verwendet wird, und JTAG (Joint Test Action Group) hieß das Gremiums, das diesen Bus standardisiert hat. )

"Automatically connect to cable and identify Boundary-Scan chain" auswählen und fertig stellen.

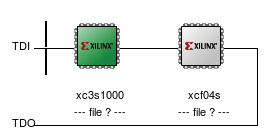

Wenn alles richtig funktioniert, wird der zu programmierende Spartan3 unter dem Namen xc3s1000 gefunden. Falls es nicht klappt, Betreuer rufen. Denn dann ist etwas falsch zusammengesteckt (ein Jumper etc.).

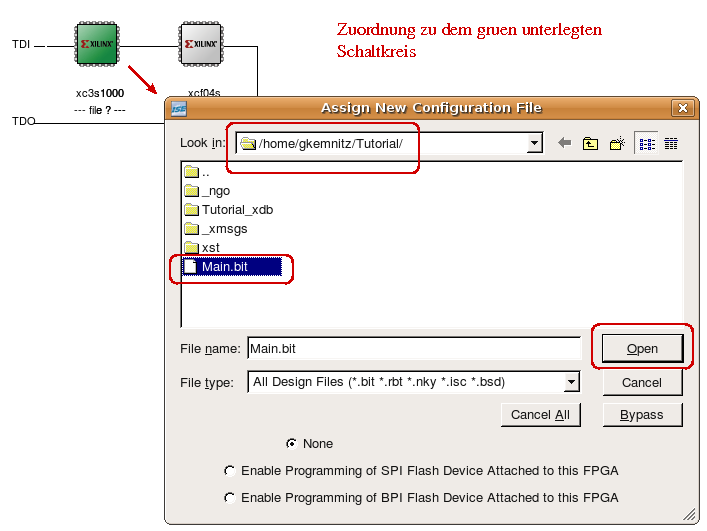

Zuordnung der Konfigurationsdatei Main.bit an den xc3s1000

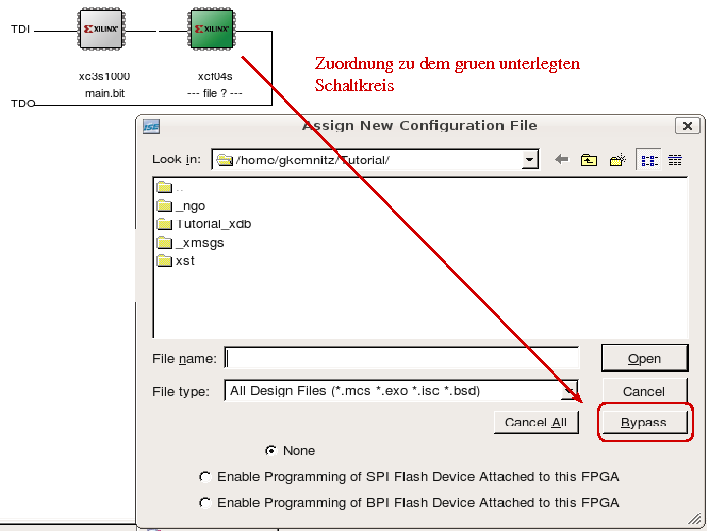

Der ander Schaltkreis in der Kette ist ein Flash-Speicher, aus den der FPGA auch gebootet werden könnte. Dazu müssen die Jumper verändert werden. Der Inhalt diese Flashes soll nicht verändert werden. Statt der Zuordnung einer Konfigurationsdatei ist "Bypass" (Überbrücken) zu wählen.

Programmieren

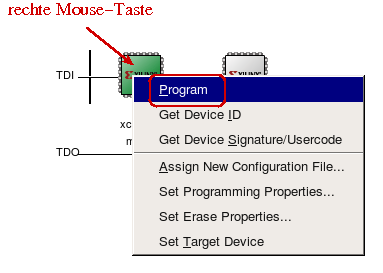

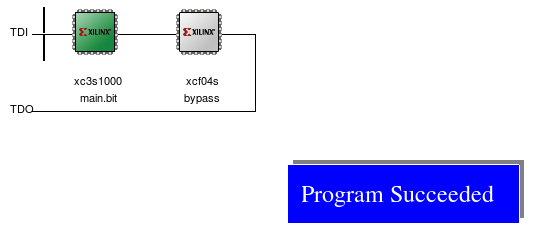

Rechts-Click auf dem Spartan (xs3s1000). Auswahl "Program...".

Wenn die nachfolgende Meldung erscheint, ist der Schaltkreis programmiert und kann getestet werden.

Test

Der Test besteht in dieser Aufgabe nur darin zu überprüfen, dass sich die Leuchtdioden mit den Schaltern richtig ein- und ausschalten lassen (zum Board-Rand ist aus/Leuchtdiode dunkel).

- Testen Sie zuerst, ob sich mit Schalter sw0 Leuchtdiode ld0 etc. schalten lässt.

- Bestimmen Sie (auf Papier) die Wertetabelle für die Ansteuerung der Leuchtdiode ld7 und überprüfen Sie, ob ihre Schaltung genauso arbeitet.

- Denken Sie sich eine andere logische Funktion mit vier Eingangsvariablen und den Operationen and, or, xor und not aus. Ändern Sie die VHDL-Datei. Übersetzen Sie neu, Laden Sie die neue Schaltung und testen Sie sie.

Design-Änderung

Ändern Sie Main.vhd so, dass auf den Leuchtdiodenausgang der negierte Wert des Tastereingangs ausgegeben wird. Übersetzen Sie das Projekt neu. Laden Sie die neue Konfiguration in den Schaltkreis und überprüfen Sie, dass der Taster genau das Entgegengesetzte bewirkt.

Bauen Sie in Main.vhd kleine Fehler ein (z.B. Semikolon durch Komma ersetzen, Buchstaben in Signalnamen oder Bezeichnern ändern etc. und machen Sie sich mit den Fehlermeldungen vertraut, die dann bei der Übersetzung erscheinen.

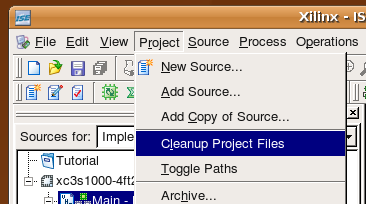

Aufräumen

Das Entwurfssystem erzeugt gewaltige Datenmengen in jedem Projekt. Geben Sie deshalb stets am Ende jeder Übung ein "Cleanup Project Files" unter dem Menüpunkt "Project". Das löscht alle Dateien, die das System jederzeit wieder neu berechnen kann. Die Design-Quellen bleiben erhalten.

Autor: gkemnitz, Letzte Änderung: 15.04.2024 16:05:19