## Prüfungsklausur Entwurf digitaler Schaltungen

**Hinweise:** Die Bearbeitungszeit beträgt 90 Minuten. Schreiben Sie die Lösungen, so weit es möglich ist, auf die Aufgabenblätter. Tragen Sie Namen, Matrikelnummer und Studiengang in die nachfolgende Tabelle ein. Zum Bestehen sind  $\geq 20$  Punkte erforderlich. Geben Sie die Aufgabenblätter zum Schluss mit ab.

| Name | Matrikelnummer | Studiengang | Punkte | ZPHÜ* | Note |

|------|----------------|-------------|--------|-------|------|

|      |                |             |        |       |      |

<sup>\*</sup> Zusatzpunkte für Hausübungen

Ich erkläre mich damit einverstanden, dass das Klausurergebnis im Internet auf der Web-Seite http://techwww.in.tu-clausthal.de/unter meiner Matrikelnummer bekanntgegeben wird.

## Unterschrift

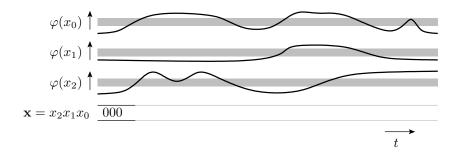

Aufgabe 1: Gegeben sind folgende Spannungsverläufe auf den Leitungen eines 3 Bit breiten Busses:

- a) Kennzeichnen Sie in der Grafik darunter die zeitlichen Bereiche, in denen der Signalwert auf dem Bus ungültig ist.

- b) Tragen Sie für alle Bereiche, in denen der Signalwert definiert ist, den Signalwert ein (positive Logik).

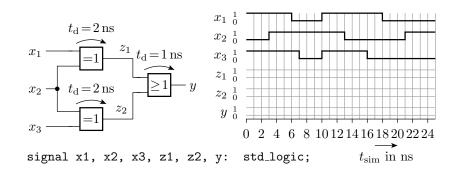

Aufgabe 2: Gegeben ist die nachfolgende Schaltung und die Verläufe der Eingangssignale.

- a) Beschreiben Sie die Schaltung in VHDL durch nebenläufige Signalzuweisungen.

- b) Schreiben Sie einen Prozess in VHDL, der die vorgegebenen Eingabesignalverläufe erzeugt. 2P

2P

2P

c) Ergänzen Sie die Verläufe der Signale  $z_1, z_2$  und y in der Abbildung. 3P

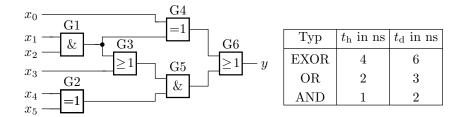

**Aufgabe 3:** Gegeben ist die nachfolgende Schaltung mit den Halte- und Verzögerungszeiten für jeden Gattertyp.

- a) Bestimmen Sie für alle Pfade durch die Schaltung die Halte- und die Verzögerungszeiten. 3P

- b) Wie groß ist die Halte- und die Verzögerungszeit der Gesamtschaltung?

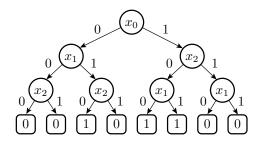

Aufgabe 4: Gegeben ist das folgende binäre Entscheidungsdiagramm:

- a) Stellen Sie die Wertetabelle auf.

- b) Wandeln Sie es in ein geordnetes binäres Entscheidungsdiagramm (OBDD) mit der Abfragereihenfolge  $x_0$ ,  $x_1$  und  $x_2$  um.

- c) Entwickeln Sie mit Hilfe der Vereinfachungsregeln aus dem OBDD in Aufgabenteil b) das zugehörige reduzierte geordnete binäre Entscheidungsdiagramm (ROBDD).

- d) Entwickeln Sie aus dem ROBDD in Aufgabenteil c) die optimierte Schaltung aus Gattern und Multiplexern.

Aufgabe 5: Entwerfen Sie ein FCMOS-Gatter mit der logischen Funktion:

$$z = \overline{x_2 (x_1 \vee \overline{x}_2 \vee x_3 \vee x_4) \vee x_4 (x_1 \vee (x_2 \wedge x_3) \vee x_4)}$$

a) Vereinfachen Sie den Ausdruck so weit wie möglich.

4.50

b) Stellen Sie die Funktionen  $f_n$  und  $f_p$  auf.

1P

1P

c) Zeichnen Sie die minimierte Transistorschaltung.

$^{2}P$

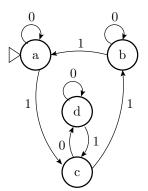

Aufgabe 6: Gegeben ist folgender Automatengraph.

Zustandscodierung:

| Zustand        | a  | b  | c  | d  |

|----------------|----|----|----|----|

| Code $s_1 s_0$ | 00 | 10 | 11 | 01 |

Die Eingabevariable sei x.

Ausgegeben wird der Zustand.

- a) Beschreiben Sie den Automaten in VHDL (komplett mit Entity und Architecture).

- b) Stellen Sie die KV-Diagramme für die Berechnung der Folgewerte von  $s_0$  und  $s_1$  auf. 2P

- c) Lesen Sie die minimierten Gleichungen für  $s_0^+$  und  $s_1^+$  ab.

- d) Setzen Sie die Gesamtschaltung des Automaten aus logischen Gattern und Speicherzellen zusammen.

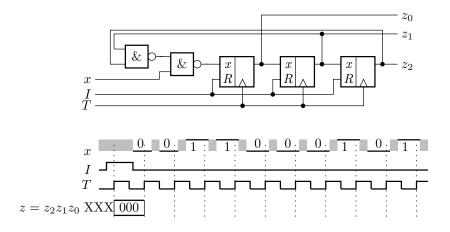

Aufgabe 7: Gegeben ist das nachfolgende rückgekoppelte Schieberegister.

- a) Stellen Sie die logischen Gleichungen zur Berechnung des Folgezustands aus dem Istzustand und der Eingabe auf.

- b) Bestimmen Sie die Ausgabefolge für den vorgegebenen Eingabesignalverlauf und ergänzen Sie ihn in der Abbildung.

- c) Wie kann der Zustand »111« verlassen werden?

1P

## Zur Bewertung:

| Aufgabe             | 1 | 2 | 3 | 4 | 5 | 6  | 7 | Summe |

|---------------------|---|---|---|---|---|----|---|-------|

| max. Punktezahl     | 4 | 7 | 4 | 7 | 4 | 10 | 4 | 40    |

| erzielte Punktezahl |   |   |   |   |   |    |   |       |